Hardware Reference

In-Depth Information

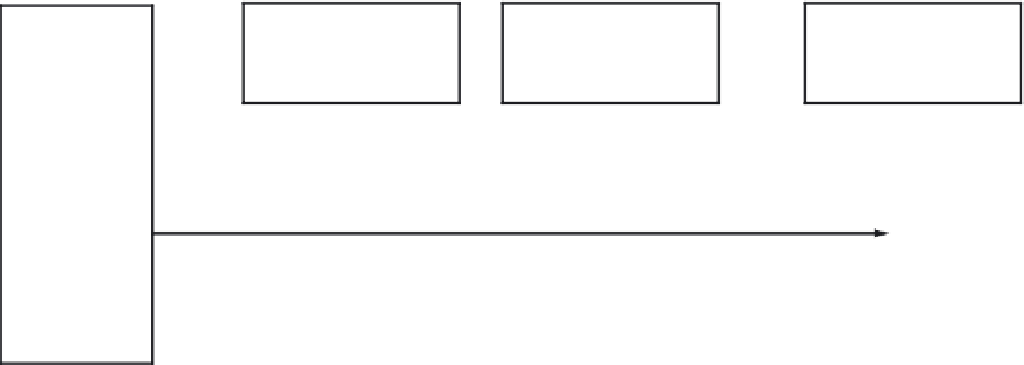

Slave 0

Slave 1

Slave

k

+5 V

Shift

register

SPI master

Shift

register

Shift

register

(HCS12)

MOSI

SCK

MISO

SS

MOSI

SCK

MISO

SS

MOSI

SCK

MISO

SS

SS

SCKx

MOSIx

MISOx

PP0

PP1

PP

k

Figure 10.9

■

Single-master and multiple-slave device connection (method 1)

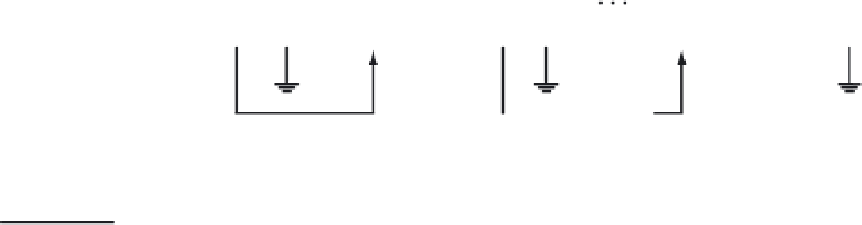

Slave 0

Slave 1

Slave

k

SPI master

(HCS12)

Shift

register

Shift

register

Shift

register

+5 V

MOSI

SCK MISO

SS

MOSI SCK MISO

SS

MOSI SCK MISO

SS

SS

SCKx

MOSIx

MISOx

Figure 10.10

■

Single-master and multiple-slave device connection (method 2)

2. The

MI

SO pin of the master is wired to the same pin of the last slave device.

3. The SS inputs of all slaves are tied to ground to enable all slaves.

Thus the shift registers of the SPI master and slaves become a ring. The data of slave

k

is

shifted to the master SPI, the data of the master is shifted to slave 0, the data of slave 0 is shifted

to slave 1, and so on. In this configuration, a minimal number of pins control a large number of

peripheral devices. However, the master does not have the freedom to select an arbitrary slave

device for data transfer without going through other slave devices.

Search WWH ::

Custom Search