Hardware Reference

In-Depth Information

Begin

End

Transfer

SS (O)

master only

SS (I)

SCK (CPOL = 0)

SCK (CPOL = 1)

Sample I

MOSI/MISO

Change O

MOSI Pin

Change O

MISO Pin

t

L

t

T

t

I

t

L

MSB first (LSBF = 0)

LSB first (LSBF = 1)

MSB

LSB

Bit 6

Bit 5

Bit 2

Bit 4

Bit 3

Bit 3

Bit 4

Bit 2

Bit 5

Bit 1

Bit 6

LSB

MSB

Minimum 1/2 SCK

for

Bit 1

t

T

,

t

I

,

t

L

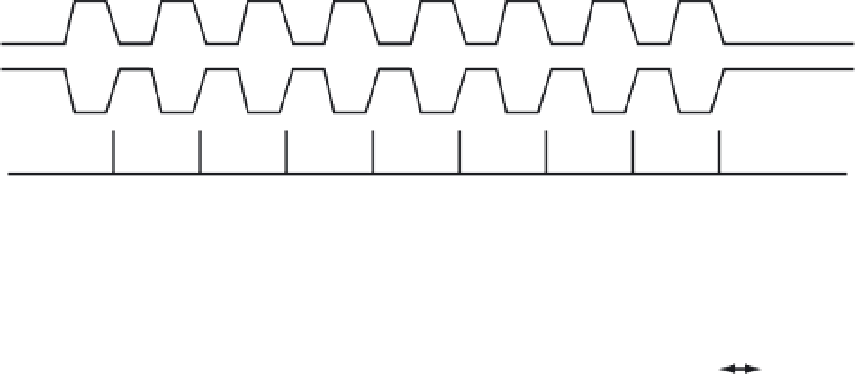

Figure 10.6

■

SPI clock format 1 (CPHA

5

1)

The SPI subsystem can be used in bidirectional mode. In this mode, the SPI uses only one

serial data pin for the interface with external device(s). The MSTR bit of the SPI

x

CR1 register

decides which pin is to be used. The MOSI pin becomes a serial data I/O (MOMI) pin for the

master mode, and the MISO pin becomes a serial data I/O (SISO) pin for slave mode. The MISO

pin in the master mode and the MOSI pin in the slave mode are not used by the SPI in bidirec-

tional mode. The possible combinations are shown in Figure 10.7.

The direction of each serial I/O pin depends on the BIDIROE bit. If the pin is configured

as an output, serial data from the shift register is driven out on the pin. The same pin is also

the serial input to the shift register. If we want to read data from a peripheral device, then the

BIDIROE bit should be cleared to 0.

The use of bidirectional mode is illustrated in Exercise 10.8.

If the SS

x

input becomes low while the SPI

x

is configured as a master, it indicates a system

error in which more than one master may be trying to drive the MOSI

x

and SCK

x

lines simul-

taneously. This condition is not permitted in normal operation. The MODF bit in the SPI

x

SR

register is set automatically, provided that the MODFEN bit in the SPI

x

CR2 is set.

Search WWH ::

Custom Search