Hardware Reference

In-Depth Information

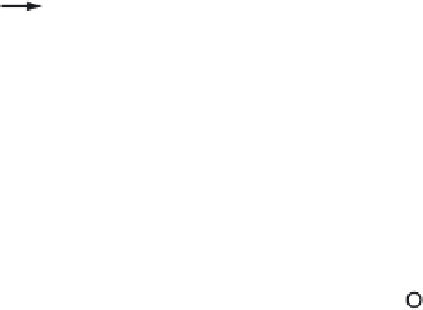

Internal bus

SCI data register

SBR12-SBR0

E-

clock

Baud divider

11-bit receive shift register

RxD

Data

recovery

H876543210L

From

TxD

Loop

control

RE

RAF

FE

NF

PE

LOOPS

RWU

M

RSRC

WAKE

Wake-up

logic

ILT

PE

PT

R8

Parity

checking

IDLE

ILIE

IDLE interrupt request

RDRF

OR

RDRF/OR interrupt request

RIE

Figure 9.14

■

SCI receiver block diagram

The transmitting device can address messages to selected receivers by including addressing

information in the initial frame or frames of each message. One can choose to use idle line or

address mark to wake up the receiver to compare the address information of the incoming frame.

I

DLE

L

INE

W

AKE

-U

P

When the idle line wake-up method is chosen, an idle condition on the RxD pin clears the

RWU bit in the SCI

x

CR2 register and wakes up the SCI. The initial frame or frames of every mes-

sage contain addressing information. All receivers evaluate the addressing information, and receiv-

ers for which the message is addressed process the frames that follow. Any receiver for which a

message is not addressed can set its RWU bit and return to the standby state. The RWU bit remains

set and the receiver remains on standby until another idle character appears on the RxD signal.

Idle line wake-up requires that messages be separated by at least one idle character and that

no message contain idle characters. The idle character that wakes a receiver does not set the

receiver idle bit, IDLE, or the receive data register full flag, RDRF.

The idle-line-type bit, ILT, determines whether the receiver begins counting logic 1s as idle

character bits after the start bit or after the stop bit. The ILT bit is in the SCI

x

CR1 register.

Search WWH ::

Custom Search