Hardware Reference

In-Depth Information

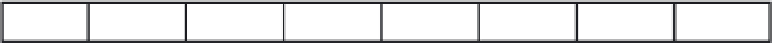

7

6

5

4

3

2

1

0

Reset value

= 0x00

TIE

TCIE

RIE

ILIE

TE

RE

RWU

SBK

TIE: transmit interrupt enable bit

0 = TDRE interrupt disabled.

1 = TDRE interrupt enabled.

TCIE: transmit complete interrupt enable bit

0 = TC interrupt disabled.

1 = TC interrupt enabled.

RIE: receiver full interrupt enable bit

0 = RDRF and OR interrupts disabled.

1 = RDRF and OR interrupt enabled.

ILIE: idle line interrupt enable bit

0 = IDLE interrupt disabled.

1 = IDLE interrupt enabled.

TE: transmitter enable bit

0 = transmitter disabled.

1 = transmitter enabled.

RE: receiver enable

0 = receiver disabled.

1 = receiver enabled.

RWU: receiver wake-up bit

0 = normal SCI receiver.

1 = enables the wake-up function and inhibits further receiver

interrupts. Normally, hardware wakes up the receiver by

automatically clearing this bit.

SBK: send break bit

0 = no break characters.

1 = generate a break code, at least 10 or 11 contiguous 0s. As long

as SBK remains set, the transmitter sends 0s.

Figure 9.10

■

SCI control register 2 (SCI0CR2/SCI1CR2)

b. Write to the SCI

x

CR1 register to configure the word length, parity, and other con-

figuration bits (LOOPS, RSRC, M, WAKE, ILT, PR, PT).

c. Enable the transmitter, interrupt, receive, and wakeup as required by writing to the

SCI

x

CR2 register bits (TIE, TCIE, RIE, ILIE, TE, RE, RWU, and SK). A preamble will

now be shifted out of the transmitter shift register.

2. Set a

transmit procedure for each character.

a. Poll the TDRE flag by reading the SCI

x

SR1 register or responding to the TDRE

interrupt.

b. If the TDRE flag is set, write the data to be transmitted to SCI

x

DRH/L, where the

ninth bit is written to the T8 bit in the SCI

x

DRH register if the SCI is in

9-bit data format. A new transmission will not result until the TDRE flag has

been cleared.

3.

Repeat step 2 for each subsequent transmission.

The contents of the SCI

x

SR1 and SCI

x

SR2 registers are shown in Figures 9.12 and 9.13,

respectively.

Setting the TE bit from 0 to 1 automatically loads the transmit shift register with a pre-

amble of 10 logic 1s (if

M

5 0) or 11 logic 1s (if

M

5 1). After the preamble shifts out, control

logic transfers the data from the SCI data register into the transmit shift register. A logic 0

Search WWH ::

Custom Search