Hardware Reference

In-Depth Information

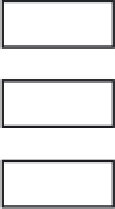

PWM module

PWM channels

Channel 7

Period and duty

Counter

PWM7

PWM

clock

E-clock

Clock select

Channel 6

Period and duty

Counter

PWM6

Control

Channel 5

Period and duty

Counter

PWM5

Channel 4

Period and duty

Counter

PWM4

Enable

Channel 3

Period and duty

Polarity

Counter

PWM3

Alignment

Channel 2

Period and duty

Counter

PWM2

Channel 1

Period and duty

PWM1

Counter

Channel 0

Period and duty

Counter

PWM0

Figure 8.38

■

HCS12 PWM block diagram

P

RESCALE

The input clock to the PWM prescaler is the E-clock. It can be disabled whenever the MCU

is in freeze mode by setting the PFRZ bit in the PWMCTL register. If this bit is set, when-

ever the MCU is in freeze mode the active clock to the prescaler is disabled. This is useful for

emulation in order to freeze the PWM. The input clock can also be disabled when all eight

PWM channels are disabled (PWME7-0 5 0). This is useful for reducing power consumption by

disabling the prescale counter.

Search WWH ::

Custom Search