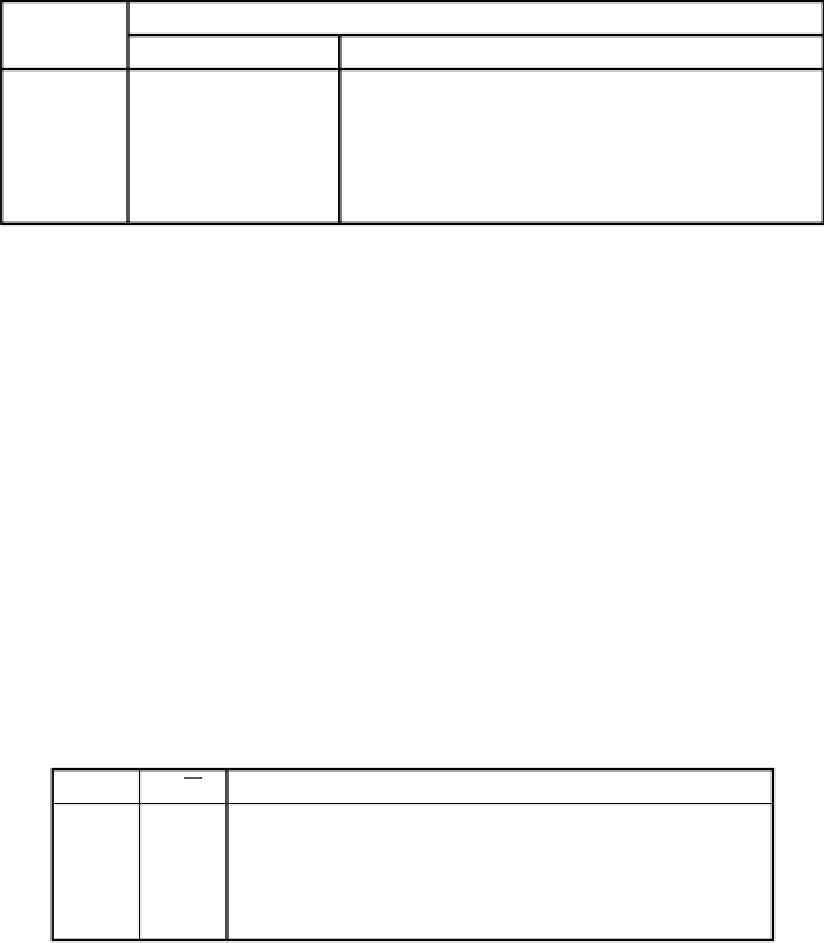

Hardware Reference

In-Depth Information

Visible

Display

Size

Character Positions

DDRAM Addresses

4

3

16

00..15

0x00..0x0F

1

0x40..0x4F

1

0x14..0x23

1

0x54..0x63

4

3

20

00..19

0x00..0x13

1

0x40..0x53

1

0x14..0x27

1

0x54..0x67

4

3

40

00..39 on 1st

controller and 00..39

on 2nd controller

0x00..0x27

1

0x40..0x67 on 1st controller and

0x00..0x27

1

0x40..0x67 on 2nd controller

Note: Two LCD controllers are needed to control LCD displays with 4

3

40 characters.

Table 7.7c

■

DDRAM address usage for a four-line LCD

The HD44780U has two 8-bit registers, an

instruction register

(IR) and a

data register

(DR).

The IR stores

instruction codes

, such as

display clear

and

cursor move,

and

address information

for display data RAM (DDRAM) and character generator RAM (CGRAM). The microcontroller

writes commands into this register to set up the LCD operation parameters. To write data into

the DDRAM or CGRAM, the microcontroller writes data into the DR. Data written into the

DR will be automatically written into DDRAM or CGRAM by an internal operation. The DR

is also used for data storage when reading data from DDRAM or CGRAM. When address infor-

mation is written into the IR, data is read and then stored in the DR from DDRAM or CGRAM

by an internal operation. The microcontroller can then read the data from the DR. After a read

operation, data in DDRAM or CGRAM at the next address is sent to the DR and the microcon-

troller does not need to send another address. The IR and DR are distinguished by the RS signal.

The IR is selected when the RS input is low. The DR is selected when the RS input is high.

Register selection is illustrated in Table 7.8.

RS

R/W

Operation

0

0

IR write as an internal operation (display clear, etc.).

0

1

Read busy flag (DB7) and address counter (DB0 to DB6).

1

0

DR write as an internal operation (DR to DDRAM or CGRAM).

1

1

DR read as an internal operation (DDRAM or CGRAM to DR).

Table 7.8

■

Register selection

B

USY

F

LAG

(BF)

The HD44780U has a busy flag (BF) to indicate whether the current internal operation is

compl

ete

. When BF is 1, the HD44780U is still busy with an internal operation. When RS 5 0

and R/W is 1, the busy flag is output to the DB7 pin. The microprocessor can read this pin to

find out if the HD44780U is still busy.

A

DDRESS

C

OUNTER

(AC)

The HD44780U uses a 7-bit address counter to keep track of the address of the next

DDRAM or CGRAM location to be accessed. When an instruction is written into the IR, the

address information contained in the instruction is transferred to the AC register. The selection

Search WWH ::

Custom Search