Hardware Reference

In-Depth Information

R

EDUCED

D

RIVE

R

EGISTER

(RDRIV)

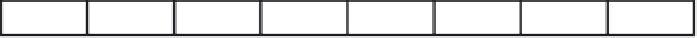

This register is used to select reduced drive for the pins associated with the core ports,

which gives reduced power consumption and reduced RFI with a slight increase in transition

time, a feature used on ports that have a light loading. This register is not in the memory map

in expanded mode. The contents of the register are shown in Figure 7.5.

7

6

5

4

3

2

1

0

Reset value

= 0x00

RDPK

0

0

RDPE

0

0

RDPB

RDPA

RDPK: reduced drive of Port K

0 = all Port K pins have full drive enabled.

1 = all Port K pins have reduced drive enabled.

RDPE: reduced drive of Port E

0 = all Port E pins have full drive enabled.

1 = all Port E pins have reduced drive enabled.

RDPB: reduced drive of Port B

0 = all Port B pins have full drive enabled.

1 = all Port B pins have reduced drive enabled.

RDPA: reduced drive of Port A

0 = all Port A pins have full drive enabled.

1 = all Port A pins have reduced drive enabled.

Figure 7.5

■

Reduced Drive register (RDRIV)

E

XTERNAL

B

US

I

NTERFACE

C

ONTROL

R

EGISTER

(EBICTL)

Only the bit 0 (ESTR) of this register is implemented. It controls the stretching of the ex-

ternal E-clock. When the ESTR bit is set to 0, the E-clock is free running and does not stretch

(lengthen). When the HCS12 is interfacing with a slower memory device, then the E-clock can

be lengthened (have its high interval stretched) by setting this bit.

Port K has a Port K data register (PORTK or PTK) and a data direction register (DDRK).

In the expan

ded

mode, Port K carries the ex

pand

ed address XADDR14,XADDR19, emulated

chip-select (ECS), and external chip-select (XCS) signals. The PK6 pin is available only in the

H subfamily. The functions of Port K pins are shown in Figure 7.6. At the rising edge of the

PK0/X14

PK1/X15

PK2/X16

PK3/X17

PK4/X18

PK5/X19

PK6/XCS (only available in H subfamily)

PK7/ECS/ROMONE

Figure 7.6

■

Port K pins and their alternate functions

Search WWH ::

Custom Search