Hardware Reference

In-Depth Information

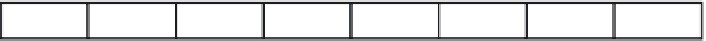

7

6

5

4

3

2

1

0

PLLSEL

PSTP

SYSWAI ROAWAI

PLLWAI

CWAI

RTIWAI COPWAI

Reset:

0

0

0

0

0

0

0

0

PLLSEL: PLL select bit

0 = System clocks are derived from OSCCLK.

1 = System clocks are derived from PLLCLK.

PSTP: pseudo-stop bit

This bit controls the functionality of the oscillator during the stop mode.

0 = Oscillator is disabled in stop mode.

1 = Oscillator continues to run in stop mode (pseudo mode). The oscillator amplitude

is reduced.

SYSWAI: system clocks stop in wait-mode bit

0 = The system clocks continue to run in wait-mode.

1 = The system clocks stop.

ROAWAI: reduced oscillator amplitude in wait-mode bit

0 = normal oscillator amplitude in wait mode.

1 = reduced oscillator amplitude in wait mode.

PLLWAI: PLL stops in wait mode bit

0 = PLL keeps running in wait mode.

1 = PLL stops in wait-mode. The CRG will clear the PLLSEL bit before entering wait

mode. The PLLON bit remains set during wait mode but the PLL is powered

down.

CWAI: core stops in wait-mode bit

0 = Core clock keeps running in wait mode.

1 = Core clock stops in wait mode.

RTIWAI: RTI stops in wait-mode bit

0 = RTI keeps running in wait mode.

1 = RTI stops and initializes the RTI dividers whenever the part goes into wait mode.

COPWAI: COP stops in wait-mode bit

0 = COP keeps running in wait mode.

1 = COP stops and initializes the COP dividers whenever the part goes into wait

mode.

Figure 6.13

■

The CRG clock select register (CLKSEL)

The PLL can change the bandwidth or operational mode of the loop filter manually or

automatically. In

automatic bandwidth control

mode (the AUTO bit of the PLLCTL regis-

ter is set to 1), the lock detector automatically switches between acquisition and tracking

modes. The automatic bandwidth control mode is also used to determine when the PLL clock

(PLLCLK) is safe to use as the source for the system and core clocks. When the LOCK bit of the

CRGFLG register is set to 1, the PLLCLK signal can be used as the system clock safely. The

setting of the LOCK bit can be detected by using the interrupt or polling method. Any change

of the LOCK bit will cause the LOCKIF flag bit to be set to 1 and may optionally request an

interrupt to the CPU.

The PLL circuit can also operate in

manual

mode (AUTO bit 5 0). The manual mode is

used by systems that do not require an indicator of the lock condition for proper operation.

Such systems typically operate well below the maximum system frequency (

f

sys

) and require

fast startup. To operate in manual mode, we must observe the following procedure:

1. Assert the ACQ bit (in PLLCTL register) before turning on the PLL manual mode.

This configures the filter in acquisition mode.

Search WWH ::

Custom Search