Biomedical Engineering Reference

In-Depth Information

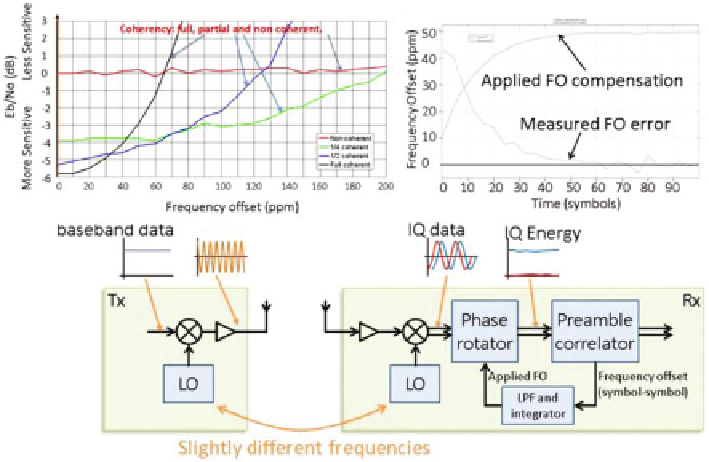

Fig. 20

Closed-loop frequency tracking for coherent reception

and the code phase of the preamble symbols. The longer the synchronization takes,

the more power consumption it needs, leading to less duty-cycling efficiency. Another

power overhead to reduce the duty-cycling efficiency is the startup behavior of the

analog/RF circuit [

16

]. For efficient duty-cycling, fast start-up is required for each

individual block in the receiver. The start-up time is mainly improved by storing the

biasing information in large capacitors. For circuit like VGA where the accuracy of

the bias current is very critical, the restoring of the biasing information is calibrated,

whereas for RF blocks the restoring is noncalibrated. Other than block-level startup

optimization, the connections between the blocks are also critical regarding the

startup behavior. Obviously, AC coupling becomes less attractive as compared to

DC coupling, which however suffers from DC offset. Therefore, offset calibration

scheme becomes necessary and critical in the system design, with minimum hardware

overhead.

Measurement Results and Conclusions

The complete transmitter, receiver front-end, and ADC are taped out in 90 nm CMOS

technology and the die photos are shown in Fig.

21

.

The wireless link is evaluated at 8 GHz with a bandwidth of 499.2 MHz and

data rate of 0.85 Mbps. The first evaluation is done with the transmitter and the

receiver front-end. The down converted baseband data from the receiver front-end

Search WWH ::

Custom Search