Cryptography Reference

In-Depth Information

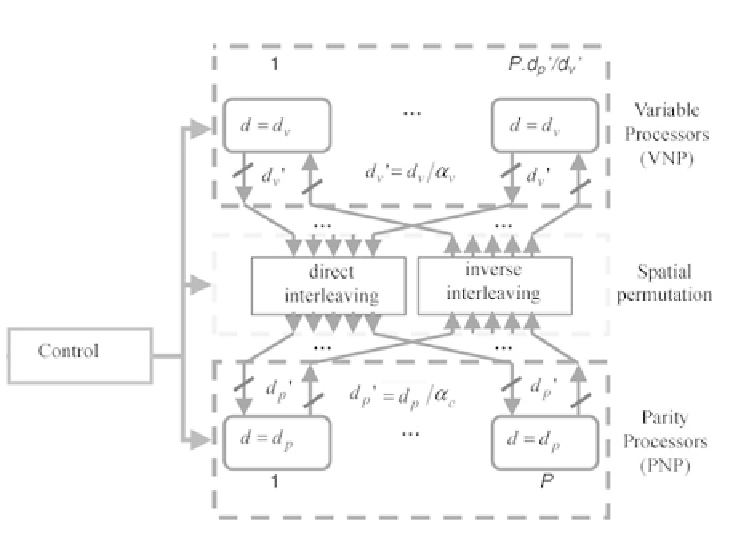

Figure 9.13 - Generic serial-parallel architecture.

makes it possible to randomly access the nodes associated with a same processor

of nodes, by memory addressing, for example. The combination of these two

types of permutations enables a random interconnection such as that existing

between the variable nodes and the parity nodes of the LDPC code.

Example of an implementation

To help clarify ideas about the way to organize the computations and the propa-

gation of the messages in the decoder, and to truly understand the link between

the organization of the propagation of the messages and the structure of the

LDPC code, Figure 9.14 shows a simple example of decoding an LDPC code of

length

n

=12

and rate

R

=0

,

5

(therefore

m

=6

), with

P

=2

,

d

c

=3

,

α

=1

and

β

=

d

v

. There are therefore

P

=2

parity node processors and

n/P

=6

variable node processors. One iteration is performed in

m/P

=3

steps:

•

At the first cycle, reading the information relative to the bits is done in

each of the VNPs, each of them containing

n/P

=2

bits of the codeword

(in practice,

n/P

can be much higher). These bits are shaded in grey in

each VNP: this is space permutation.