Graphics Reference

In-Depth Information

a

b

data

1

data

2

data

m

ctx

1

ctx

2

ctx

m

State (Multi-Symbol)

Read State

Update

Range

Range

Range

MUX

Update

Low

Low

Low

MUX

Update

Output

Output

Output

Write State

State Memory

output

2

output

m

output

1

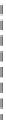

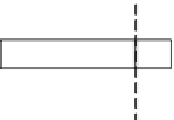

Fig. 11.20

Multi-bin (

a

) overall block diagram (

b

) state forwarding circuit

M

M

M

L

L

L

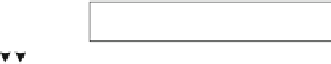

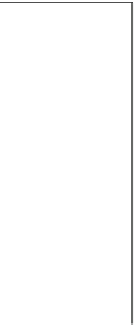

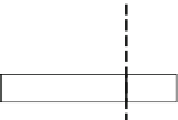

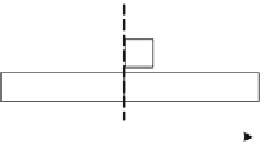

Fig. 11.21

Simplified architecture of multi-bin binary arithmetic encoder

State Stage

Range Stage

Low Stage

Output Stage

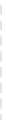

M

M

M

M

L

L

L

L

Time

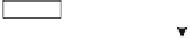

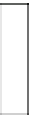

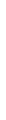

Fig. 11.22

Branch imbalance of four-stage pipeline architecture in H.264/AVC [

11

]

The effectiveness of cascading technique is still limited because of growing

delay in state forwarding circuit as the number of cascading stages increase. The

operating frequency will be reduced if too many cascading stages are used. For

higher throughput, a ML-decomposed architecture may be applied as follows [

11

].

We can observe from the CABAC pipeline that the complexity for processing the

MPS and LPS in each stage is different. We can divide the processing into two

parts: M for MPS and L for LPS for timing analysis. A typical multi-bin CABAC

architecture is shown in Fig.

11.21

. After analysis, we can observe the imbalance as

indicated in Fig.

11.22

. The MPS and LPS have different latencies. To have higher

throughput, we may divide the arithmetic into two separate coders.