Hardware Reference

In-Depth Information

b

x

0

x

1

x

2

x

3

x

4

x

5

x

6

x

7

a

E

1

E

2

E

3

E

4

E

5

E

6

E

7

E

8

E

9

1

1

0

1

1

0

0

0

*

*

T

i

m

e

s

t

e

p

t 9

2

1

0

1

0

0

1

0

0

1

3

0

1

1

0

0

0

1

0

0

E

1

E

2

E

3

4

1

*

0

1

0

0

0

1

1

5

0

1

0

1

1

0

0

0

*

E

4

E

5

E

6

6

0

1

1

0

0

0

1

0

0

7

1

0

1

0

0

1

0

0

1

8

1

0

0

1

0

0

0

1

1

E

7

E

8

E

9

0

1

0

1

1

0

0

0

*

c

x

0

x

1

f(E

1

)=x

0

f(E

2

)=x

0

f(E

3

)=x

1

f(E

4

)=x

1

f(E

5

)=x

0

·

x

1

f(E

6

)=x

0

·

x

1

f(E

7

)=x

0

·

x

1

f(E

8

)=x

0

·

x

1

f(E

9

)=x

0

t

x

0

10

1

0

1

0

0

1

1

0

x

1

0

1

1

0

0

1

1

0

0

2

3

4

5

6

7

8

9

E

1

E

2

E

3

E

4

E

5

E

6

E

7

E

8

E

9

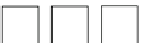

Fig. 1.16

(

a

) Actuation sequences to be applied on electrode; (

b

) broadcast-addressing biochip

with 9 control pins; (

c

) pin-constrained biochip with control circuit

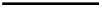

1.2.5

Chip-Level Design

The above discussion highlighted the design flow for digital microfluidic biochips.

This design flow includes four stages, i.e., (1) high-level synthesis, (2) droplet

routing, (3) derivation of the pin-assignment configuration, and (4) derivation of the

wire-routing solution. Figure

1.17

a illustrates the overall design flow [

55

]. “Fluidic-

level synthesis” (which includes Stages 1 and 2) and “physical design” (which

includes Stages 3 and 4) are optimized separately.

An integrated design flow of a biochip, which aims at filling the gap between

fluidic-level synthesis and chip-level design, is proposed in [

55

]. The conventional

and proposed design flows in [

55

] are compared in Fig.

1.17

.