Hardware Reference

In-Depth Information

7.4

Simulation Results

7.4.1

Results Derived by the Operation-Interdependency-

Aware Synthesis Approach

In Sect.

4.5.3

, we have mapped bioassays to direct-addressing biochips with dif-

ferent sizes. The corresponding completion times of bioassays in dilution/mixing

(D/M) phases and transportation (T) phases on the direct-addressing biochips are

shown in Table

4.5

.

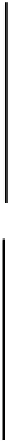

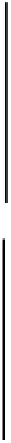

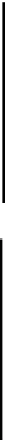

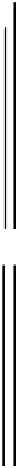

As discussed in Sect.

6.6

, we can map bioassays to pin-limited general purpose

biochips proposed in [

3

,

4

]. The pin-assignment configurations for 8

8, 9

9,

10

8,and12

8 electrode arrays are shown in Fig.

7.4

. Compared with the direct-

addressing scheme, the design of pin-limited general-purpose biochips can reduce

the pin-counts by 50.0-65.8 %.

The synthesis results for executing bioassays on direct-addressing biochips are

defined as “initial results”. By applying the scheduling algorithm proposed in [

4

]on

the initial results, we derive the synthesis results for bioassays. Hence the bioassays

can be mapped to the general-purpose pin-limited biochips shown in Fig.

7.4

.The

corresponding completion times of bioassays in D/M phases and T phases on these

pin-limited general-purpose biochips are shown in Table

7.1

. The clock frequency

of the T phase is also set as 1 Hz.

b

a

18 36 20 26 29 21 2 3 4

3 5 89 65167

37 32 21 19 22 4 8 9 10

27 6 301725111213 2

36 34 31 2 26 14 3 15 16

12 16 20 23 27 10 5 17 18

24 35 32 11 15 19 20 7 8

30 7 33 29 24 1 13 14 21

372212 6 2818222324

03 5 32134

19 8 45678

32 26 19 14 4 9 10 11

22 23 6 21 12 13 2 14

4 16292515 8 1617

27 20 11 26 1 18 19 3

28 30 12 24 10 20 5 13

25 7 182717212211

c

d

32 2 37 34 8 30 25 19 21 22

27 38 17 33 29 22 23 2 3 4

0 01 1 7 35167

21 35 11 15 19 24 4 8 9 10

31 9 22 32 6 18 11 12 13 2

5 163420282514 3 1516

37 36 14 1 29 26 10 5 17 18

28 7 242116121920 7 8

31

7

41 37 39

3

33 17 23 26

1

20

24 42 40 17 11 35 19 30

4

22 21 16

26 28

5

20 34 31 10 25

2

15 17

9

6

39 29 36 30

1

27 24 20 18 12

6

40 38 31 32 13 28 12 22 19

7

8

2

35 12

4

16 18 25 11

5

13

9

3

1

14 37 33 27 29 21 23

8

14 10

4

5

2

32 34 26 14

3

24 16 15 11

6

7

Fig. 7.4

Pin-assignment configuration for: (

a

) 8

8 array; (

b

) 9

9 array; (

c

) 10

8 array; and

(

d

) 12

8 array