Hardware Reference

In-Depth Information

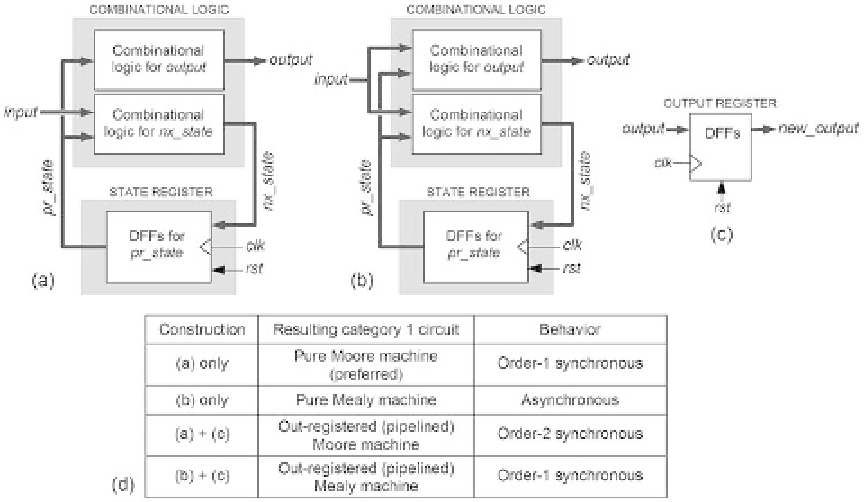

Figure 5.2

Regular (category 1) state machine architectures for (a) Moore and (b) Mealy types. (c) Optional

output register. (d) Resulting circuits.

Regular Mealy machine

(i gure 5.2b): In this case, the input is connected to both

logic blocks, so it can affect the output directly, resulting an asynchronous behavior.

Therefore, the machine can have more than one output value for the same state

(section 3.5).

Out-registered (pipelined) Moore machine:

This consists of connecting the register of

i gure 5.2c to the output of the Moore machine of i gure 5.2a. As seen in sections 2.5

and 2.6, two fundamental reasons for doing so are glitch removal and pipelined con-

struction. As a result, the i nal circuit's output will be delayed with respect to the

original machine's output by either one clock period (if the same clock edge is

employed in the state register and in the output register) or by one-half of a clock

period (if different clock edges are used). Note that the resulting circuit is order-2

synchronous because the original Moore machine was already a registered circuit (in

other words, the input-output transfer occurs after two clock edges—see details in

section 3.5). If in a given application this extra register is needed but its consequent

extra delay is not acceptable, the next alternative can be used.

Out-registered (pipelined) Mealy machine:

This consists of connecting the register of

i gure 5.2c to the output of the Mealy machine of i gure 5.2b. The reasons for

doing so are the same as for Moore machines. The resulting circuit is order-1 synchro-

nous because the original Mealy machine is asynchronous. Consequently, the overall