Hardware Reference

In-Depth Information

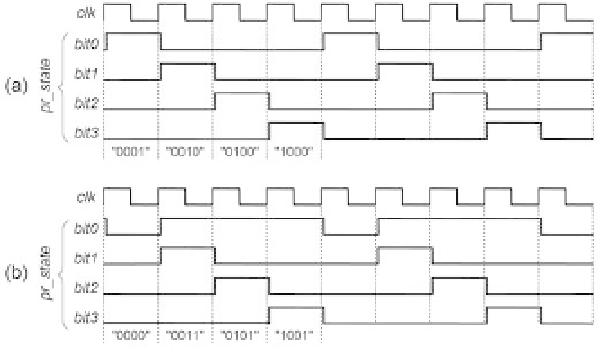

In a Gray code, each codeword is obtained by modifying the value of the rightmost

bit in the previous codeword such that a new codeword results (see i gure 3.9a). For

the type

state

above, three bits would be needed, resulting in A = “000”, B = “001”, C

= “011”, D = “010”, and E = “110”.

Just to illustrate the Gray code, a Gray counter is presented in i gure 3.9b, which

consists simply of a regular sequential counter whose output is converted into Gray

code by means of the following expressions (see XOR gates in

i gure 3.9b):

q(N

−

1

)

Gray

=

q(N

−

1

)

Seq

;

q(i)

Gray

=

q(i

+1

)

Seq

⊕

q(i)

Seq

for

i

=

N

−

2 to

i

= 0.

3.7.5 Modifi ed One-Hot Encoding with All-Zero State

Figure 3.10a shows an example using the true one-hot code described above for a

four-bit system (a four-state FSM). As expected, the bits of

pr_state

are {“0001”, “0010”,

“0100”, “1000”}. A modii ed version, with bit zero inverted, is depicted in

i gure 3.10b.

The encoding is now {“0000”, “0011”, “0101”, “1001”}, thus containing the all-zero

codeword. This code has the same properties as the true one-hot code in the sense

that it too has a Hamming distance of 2 between any two codewords, and all code-

words can be identii ed based on a single bit.

The alternative of i gure 3.10b is used, for example, by Altera's Quartus II compiler

when synthesizing state machines using the one-hot option. The reason for doing so

is that all DFFs in Altera's FPGAs (and Xilinx's as well for that matter) are initialized

to a low output on power-up, so if an explicit reset port was not included in the design,

the machine will still be able to start from a specii c state, avoiding improper initial-

ization and deadlock. More details on this are seen in sections 3.8 and 3.9, which

discuss the importance of reset in FSMs and how to implement safe FSMs.

Figure 3.10

(a) True one-hot encoding. (b) Modii ed one-hot encoding (bit zero inverted), containing the

all-zero codeword.