Hardware Reference

In-Depth Information

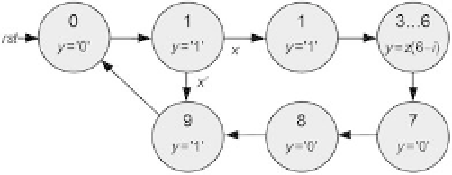

Figure 15.7

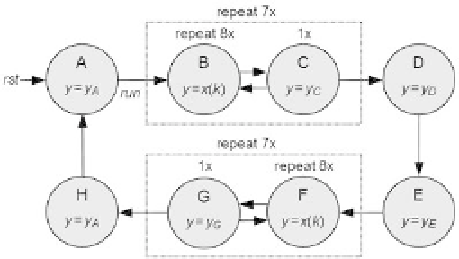

Figure 15.8

15.6 Exercises

Exercise 15.1: Number of Flip-Flops

How many DFFs are needed to build the FSMs of i gures 15.1, 15.2, and 15.6?

Exercise 15.2: Two-Loop FSM

Figure 15.7 shows a two-loop FSM, with input

x

and output

y

. When in state 3…6 the

machine must transmit four bits from a

z

(3:0) array, starting with the MSB.

a) How many l ip-l ops are needed to construct this FSM? Does your answer depend

on the implementation approach (generic, seen in the previous chapters, or pointer-

based, seen here)?

b) Implement it using VHDL or SystemVerilog (pointer-based technique). Enter

z

in

your code as a constant. After compilation, check whether the number of l ip-l ops

inferred by the compiler matches your prediction.

c) Show simulation results.

Exercise 15.3: FSM with Repetitive States

Figure 15.8 shows an FSM with an

apparent

single loop. Note that state B must be

repeated 8 times, then state C must occur, with this sequence (B-C) repeated 7 times

before proceeding to state D. A similar procedure must occur in states F-G.