Hardware Reference

In-Depth Information

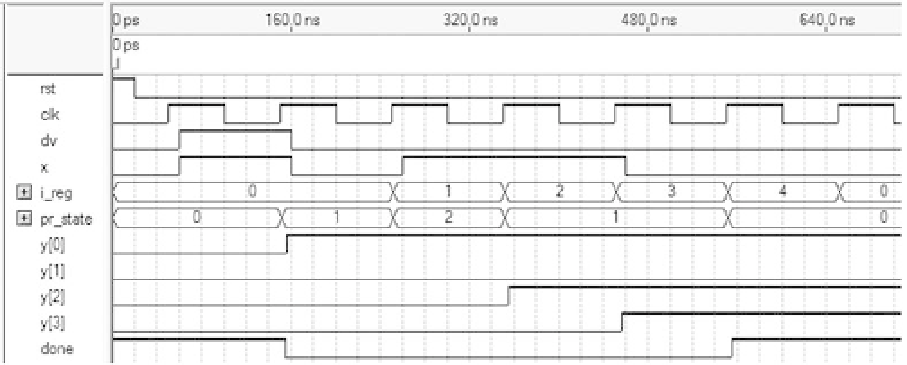

Figure 12.2

Simulation results from the VHDL code for the serial data receiver of i gure 11.14d, with

N

= 8.

In this kind of application glitches during clock transitions are generally not a

problem. In any case, because

y

is one of the signals that go through an auxiliary

register, if a glitch-free/pipelined output is required we can simply send out

y_reg

instead of

y

.

Observe the correct use of registers and the completeness of the code, as described

in comment number 10 of section 6.3.

The number of l ip-l ops inferred by the compiler on synthesizing the code below,

with regular sequential encoding (section 3.7), was 14 for

N

= 8 and 40 for

N

= 32.

Simulation results are shown in i gure 12.2, for

x

=“1011”.

1 --------------------------------------------------------

2 library ieee;

3 use ieee.std_logic_1164.all;

4 --------------------------------------------------------

5 entity serial_data_receiver is

6 generic (N: natural := 4); --number of bits (any >0)

7 port (

8 x, dv, clk, rst: in std_logic;

9 done: out std_logic;

10 y: buffer std_logic_vector(N-1 downto 0));

11 end entity;

12 --------------------------------------------------------

13 architecture moore_fsm of serial_data_receiver is

14

15

--FSM-related declarations:

16

type state is (idle, store0, store1);

17

signal pr_state, nx_state: state;

18

19

--Auxiliary-register-related declarations:

20

signal y_reg: std_logic_vector(N-1 downto 0);