Hardware Reference

In-Depth Information

11.8 Exercises

Exercise 11.1: Machines Category

a) Why are the state machines in i gures 11.5, 11.6, and 11.7 (among others) said to

be of category 3?

b) What types of transitions (section 1.6) can category 3 machines have?

c) What differentiates category 3 from categories 1 and 2?

Exercise 11.2: Generic Counter with a Stop Value

Say that we must design a counter that starts at

x

min

and stops (and remains there)

when

x

max

is reached, only returning to the initial value and running again after a

reset pulse is applied to the circuit. As in section 11.7.1, the counter must have an

enable input (

ena

) that allows the counter to run when asserted or holds it

otherwise.

a) Draw a Moore-type state transition diagram for this counter modeled as a category

3 machine.

b) Does the number of states depend on the counting range?

c) Does the number of l ip-l ops depend on the counting range? How many are needed

to build your machine with

x

min

= 1 and

x

max

= 200?

d) Is it advantageous or necessary to use the FSM approach to design counters in

general?

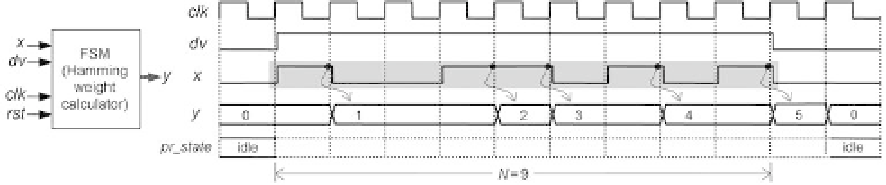

Exercise 11.3: Hamming-Weight Calculator

The circuit of i gure 11.17 must determine the Hamming weight (number of '1's) of

a

serial

bit vector

x

. The vector is delimited by a data-valid bit (the counting must

occur during all the time while

dv

= '1'). Study the illustrative timing diagram included

in the i gure. Observe that

dv

and

x

(= “100110101,” so

N

= 9) are updated at positive

clock edges and that the FSM too operates at positive clock edges (see the plot for

y

).

As usual, small propagation delays were included to portray a more realistic

situation.

Figure 11.17