Hardware Reference

In-Depth Information

The reasoning above allows us to conclude that if a circuit was modeled as a cat-

egory 3 machine (because it has recursive outputs), with all outputs requiring an

auxiliary register, then it can be implemented as if it were a category 1 circuit, with

the optional output register included. In practical terms, in such cases the “dangerous”

VHDL template of section 6.4.4 can be used (although not recommended).

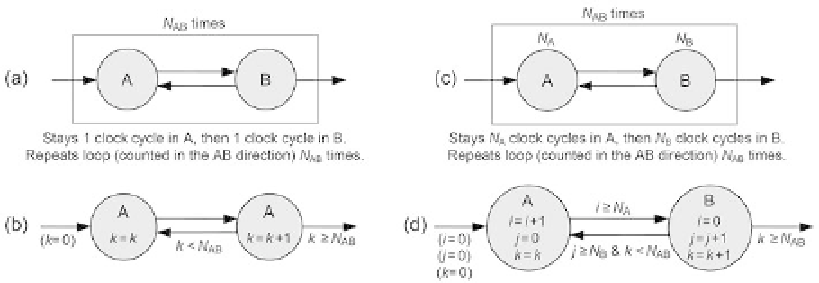

11.5 Repetitively Looped Category 3 Machines

This section highlights the particular case in which multiple pointers (counters) are

needed to implement an FSM. As is shown later in the examples, this can occur par-

ticularly when one is dealing with serial data communications (e.g., serial data receiver/

transmitter, I

2

C interface, SPI interface). Note that this section is the counterpart of

section 8.8, in which similar machines were implemented using the category 2 model.

The general problem is stated in i gure 11.4a. The machine must stay only one

clock period in each state, but the loop must be repeated

N

AB

times, where

N

AB

is the

number of times that the AB transition occurs (

N

BA

and

N

AB

+

N

BA

would be i ne too,

but an extra DFF would be required in the counter for the latter). The solution proper

is in i gure 11.4b. Note that the counter (

k

) is incremented only in state B, holding

its value while in state A.

A more general case is stated in i gure 11.4c. Here, not only must the loop be

repeated

N

AB

times, but also the machine must stay

N

A

clock periods in A and

N

B

clock

periods in B (note

N

A

and

N

B

over the state circles). The solution proper is in i gure

11.4d. Three counters (

i

,

j

,

k

) are needed. Counter

i

, which controls the stay in state

A, is incremented in A and zeroed in B. Counter

j

, which controls the stay in state B,

Figure 11.4

Repetitively looped machines using the category 3 model. (a) Symbolic representation when only

the loop must be repeated and (b) corresponding details (

k

is incremented only in state B). (c)

Symbolic representation with the loop and the individual states repeated and (d) corresponding

details (three counters are needed; again,

k

is incremented only in state B).