Hardware Reference

In-Depth Information

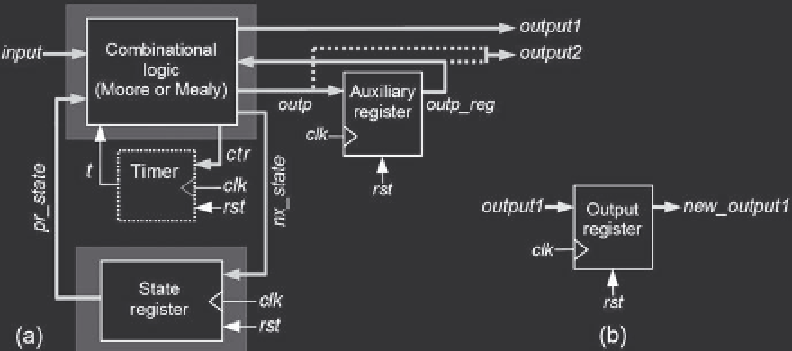

Figure 11.3

(a) General architecture for category 3 machines (timer is optional, but auxiliary register is com-

pulsory). (b) Optional output register (only for outputs not processed by an auxiliary register).

version of

outp

). On the other hand,

output1

is not registered, so depending on the

application, for it the optional output register might be needed. The resulting imple-

mentations are described below.

Recursive Moore machine

: The circuit of i gure 11.3a is used, with the input (if it exists)

connected only to the logic block for the next state, as in i gure 5.2a, and with unreg-

istered output. Regarding the options for the output, see the comments above.

Recursive Mealy machine

: Again, the circuit of i gure 11.3a is used, but this time with

the input connected to both logic blocks (for output and for next state), as in i gure

5.2b. Regarding the options for the output, see the comments above.

11.4 Category 3 to Category 1 Conversion

We said in section 1.3 that for an FSM to be implemented in hardware it must obey

three fundamental principles, the last one being that the list of outputs be exactly the

same in all states. This is indispensable because the outputs are generated by the

combinational logic section, which, being combinational, has no memory, so if an

output is not specii ed in a certain state, the compiler usually infers a latch (to hold

the output's last value), which is undesirable.

There is, however, an (apparent) exception, which occurs when the outputs are

registered

(that is, when the optional output register seen in all templates is used),

because then the outputs are stored anyway (so latches are not needed). In such cases

one might not list all outputs in all states, but that simply means that unlisted outputs

will exhibit the value previously stored in the corresponding l ip-l ops. Consequently,

for any physical purpose the list of outputs is in fact the same in all states.