Hardware Reference

In-Depth Information

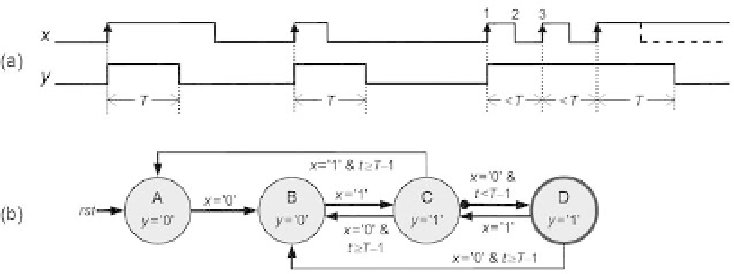

Figure 8.24

(a) Signal produced by a triggered monostable circuit (note that the output always returns to

zero). (b) A possible solution (the timer is not zeroed but it rather holds its value during the CD

transition).

A solution for the case in i gure 8.23b is presented in i gure 8.23c. Note that in this

machine, when reset is released, the output goes immediately to '1' if the input is '1',

which is i ne because this is a level-detecting machine (as opposed to edge-detecting

machines, depicted in the next example).

Monostable (one-shot) circuits are generally more complex to design than bistable

circuits. An example is shown in i gure 8.24. Observe that now

y

always returns to '0'

(initial value) after a certain time interval, regardless of

x

. As indicated by arrows in

the i gure,

y

is now edge-dependent rather than level-dependent. The output is trig-

gered by a positive transition in

x

and detriggered

T

clock cycles later. Observe that

retriggering during the time interval

T

is allowed (check the i nal part of the plot).

A solution for this problem is presented in i gure 8.24b. Note that the timer must

not be zeroed when the machine enters state D (the thick circle indicates that there

is at least one transition into state D in which the timer should not be zeroed, while

the different arrow, with a large dot at its origin, identii es that transition). Observe

also that when reset is released the output does not go to '1' if the input is '1', but it

rather waits for the next upward transition of

x

, which is proper of edge-detecting (as

opposed to level-detecting) circuits.

Solutions for edge-triggered circuits (as in i gures 8.24b) are among the few cases

in which the timer control strategy #1 (section 8.5.2) cannot be applied completely

because the timer cannot be zeroed in all state transitions (another example was seen

in section 8.8). Anyhow, it will be shown in the designs with VHDL and SystemVerilog

(sections 9.6 and 10.6, respectively) that preventing the timer from being zeroed

during specii c state transitions is very simple. Moreover, it will be shown in exercise

8.18 that this particular FSM can be broken into two FSMs, causing strategy #1 to be

applicable without restrictions.