Hardware Reference

In-Depth Information

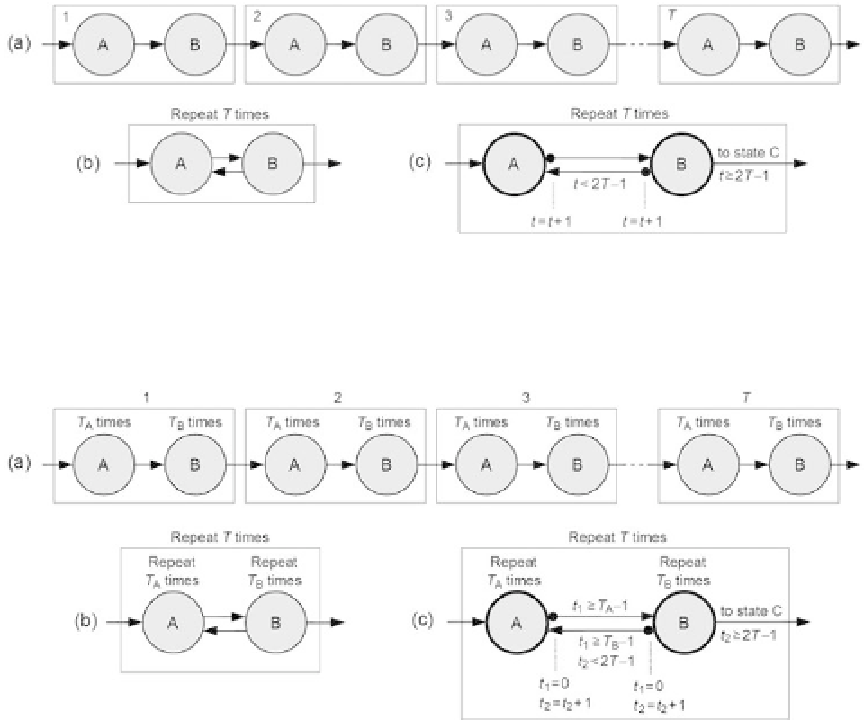

Figure 8.8

(a) FSM with a pair of states repeated

T

times. (b) Equivalent looped representation. (c) An alter-

native for the timer, counting in both directions, thus being not zeroed in any of them.

Figure 8.9

Generalization of the case seen in i gure 8.8. Not only the loop is repeated

T

times but also the

machine stays

T

A

clock periods in A and

T

B

clock periods in B.

A more general case is presented in i gure 8.9. Here, not only the loop must be

repeated

T

times, but the machine must also stay

T

A

clock periods in A and

T

B

clock

periods in B. The problem is stated in i gure 8.9a, with an equivalent representation

shown in i gure 8.9b. A possible solution is shown in i gure 8.9c, using two timers.

While timer

t

1

controls the time the machine stays in state A or state B, timer

t

2

mea-

sures the number of loop repetitions. Consequently, only timer

t

2

is not zeroed in the

state transitions.

8.8 Time Behavior of Timed Moore Machines

In section 3.5 an analysis of the general time behavior of Moore and Mealy machines

was presented. This section and the next present extensions to that analysis for the

case when timed transitions are also involved.