Hardware Reference

In-Depth Information

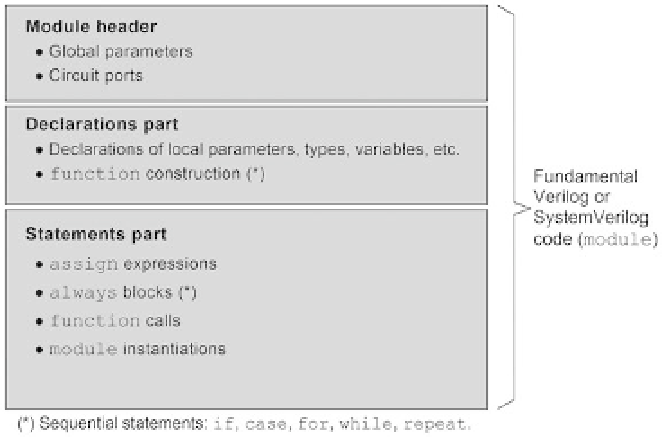

Figure 7.1

Typical SystemVerilog code structure for synthesis.

Port declarations:

This portion, similar to

port

in VHDL, is mandatory for syn-

thesis. It is just a list with specii cations of all circuit ports (I/Os), including their

mode (

input

,

output

, or

inout

), type (plus range), and name.

Declarations Part

The declarations part of a SystemVerilog code is similar to the declarative part of

architecture

in VHDL (section 6.2). It too is optional and allows all sorts of local

declarations (e.g., local parameters, data types, variables) as well as

function

(and

task

)

constructions.

Statements Part

The statements part of a SystemVerilog code is similar to the statements part of

archi-

tecture

in VHDL (section 6.2). As shown in i gure 7.1, its main elements (in no par-

ticular order) are the following:

assign

statements, normally using operators, for

simple combinational circuits;

always

blocks, constructed using sequential statements

(

if

,

case

,

for

,

while

,

repeat

), for both sequential as well as (complex) combinational

circuits;

function

(and

task

) calls; and, i nally,

module

(that is, other design)

instantiations.

7.3 SystemVerilog Template for Regular (Category 1) Moore Machines

The template is based on i gure 7.2 (derived from i gure 5.2), which shows three

always

blocks: 1) for the FSM state register; 2) for the FSM combinational logic; and