Hardware Reference

In-Depth Information

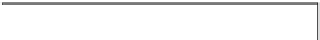

4.10 High Bandwidth Current Conveyor with Reduced R

X

An improved CMOS CCII whose design was optimized using a heuristic algorithm

for optimal sizing to achieve good static and dynamic performances was proposed

by Salem et al. [

46

] and is shown in Fig.

4.10

.

In this configuration, the main modification is the introduction of a new type of

signal path for the current transfer between ports X and Z which ensures very low

impedance looking into port X. It has been deduced [

46

] that the parasitic input

impedance R

X

is given by:

1

1

R

X

¼

ð

4

:

12

Þ

g

m

8

1

ð

þ

g

m

2

r

02

Þ

g

m

5

1

ð

þ

g

m

4

r

04

Þ

As compared to the conventional CMOS CCII, the above expression leads to a quite

reduced value of R

X

. The algorithm used by the authors was set up for minimizing

X-port input resistance, maximizing Y and Z port resistances, maximizing the 3 dB

bandwidths of the current and voltage transfers and minimizing the noise effects

and silicon area. With DC bias current of 100

A, the 3 dB bandwidth of the voltage

gain (0.96) was found to 3.9 GHz, that of the current gain (0.976) as 2.6 GHz while

the parasitic impedance levels were found to be R

X

¼

ʼ

18.47

Ω

;R

Z

||C

Z

¼

34.5 k

Ω

||

9.45 fF and R

Y

||C

Y

¼

25.25 k

Ω

||49.7 fF.

+V

DD

M

10

M

9

M

15

M

8

M

7

M

1

M

2

Z

X

Y

I

B

M

3

M

4

M

6

M

5

M

13

M

12

M

11

M

14

−V

SS

Fig. 4.10 The improved translinear based CCII structure implementation advanced by Salem

et al. (Adapted from [

46

]

2006 Springer)

©

Search WWH ::

Custom Search