Hardware Reference

In-Depth Information

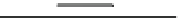

a

+V

DD

M

3

M

4

M

7

M

9

M

8

M

5

M

6

Y

M

1

M

2

X

Z

I

B

I

B

I

B

2I

B

V

B

M

12

M

10

M

11

M

13

−V

SS

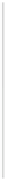

b

+V

DD

M

4

M

3

M

14

M

7

M

9

M

8

M

5

M

6

M

2

M

1

Z

Y

X

I

B

I

B

M

11

M

15

2I

B

V

B

M

10

M

12

M

13

−V

SS

Fig. 4.9 High accuracy CMOS current conveyors proposed by Hassanein et al. (a) The first

proposed high accuracy CCII+ (b) High accuracy CCII+ with adaptive offset cancellation

(Adapted from [

44

]

©

2004 Elsevier GmbH)

SPICE simulation results have demonstrated that the topology of Fig.

4.9a

has a

voltage gain of 1.00003, current gain of 1.000001 with their 3-dB bandwidth being

1.15 and 15 MHz respectively; R

x

is as small as 0.037

Ω

and input voltage range is

0.4-0.8 V, with voltage offset variation from 0.00027 to 0.071 mV only. On the

other hand, the CCII with adaptive offset cancellation has both voltage gain and

current gain of unity with their 3-dB bandwidths being 0.48 and 2.16 MHz with

voltage offset variation from 0 to 0.00026 and R

x

¼0.06

Ω

.

Search WWH ::

Custom Search