Hardware Reference

In-Depth Information

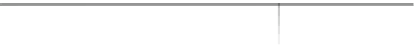

PMOS

CM1

+V

PMOS

CM2

+V

M

n2

M

p3

M

p2

M

n7

M

n3

X

Z

i

x

i

z

Y

M

p4

M

p1

M

n1

V

B

M

n6

M

n5

M

n4

−V

Fig. 4.3 An equivalent representation of the CMOS CCII+ circuit proposed by Cheng and

Toumazou [

9

]

When this circuit was simulated in HSPICE biased with 3 V DC supply, at

terminal-Y the circuit exhibited almost an infinite input resistance whereas

terminal-X exhibited a very low and almost linear input resistance which was

found to be of the order of 1.9

Ω

(DC to 100 KHz). As the input signal frequency

is increased R

x

increases to 3.9

at 10 MHz. The voltage gain

between ports Y and X exhibited a bandwidth around 13 MHz whereas the

bandwidth of the current gain between port Z and X was found to be around

10 MHz.

Ω

at 1 MHz and 37.4

Ω

4.4 Class AB First Generation Current Conveyors

The traditional class AB CMOS current conveyor shown in Fig.

4.4a

suffers from

the drawback of poor control of quiescent current level as there is no mechanism for

setting up the intended DC bias current in the circuit. To circumvent this problem,

Bruun in [

10

] presented a CMOS architecture which contains an elegant bias

stabilization scheme. This circuit is shown in Fig.

4.4b

. This circuit incorporates

a way to stabilize the quiescent current which consists of feeding back only a

fraction

1 of the X-input branch current to the Y-input branch current and

providing the remaining part of the Y-input branch current as a fixed current I

ss

to

the level shifting transistors M

1

and M

2.

As a consequence, the quiescent current

level in each branch is equal to

ʻ

FB

<

Search WWH ::

Custom Search