Hardware Reference

In-Depth Information

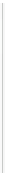

a

+V

DD

+V

DD

M

4

M

5

M

7

M

8

M

3

M

6

NMOS CM1

−V

SS

−V

SS

M

9

M

10

NMOS CM2

−V

SS

−V

SS

PMOS Current Repeater

+V

DD

I

Z

= I

X

M

1

M

2

Z

I

X

V

x

X

V

y

Y

R

X

I

B

I

B

−V

SS

NMOS CM1

−V

SS

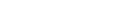

b

+V

DD

PMOS Current Repeater

I

B

I

Z

= −I

X

M

1

M

2

Z

I

X

V

x

X

V

y

Y

R

X

I

B

−V

SS

NMOS CM2

NMOS CM1

−V

SS

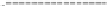

Fig. 4.2 CMOS based CCII+ and CCII

configurations proposed by Surakampontorn et al. [

5

]

Search WWH ::

Custom Search