Hardware Reference

In-Depth Information

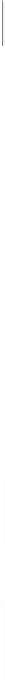

Fig. 4.1 Equivalent

representations of the

simple CMOS current

conveyors proposed by

Sedra et al. [

1

]

a

+V

PMOS

Current

Mirror

M

1

y

+

i

z

= i

x

z

i

x

A

x

−

M

2

NMOS

Current

Mirror

−V

b

+V

+V

M

1

y

+

i

z

= −i

x

z

i

x

A

x

−

M

2

−V

−V

exhaustive repertoire of circuits available, we have chosen here only those archi-

tectures which have optimized one or more of the following important parameters

or performance characteristics of the CCs such as: reduced DC power supply

requirements, reduced power consumptions, high precision, reduced parasitic

input resistance of the x-port, high current driving capability, high bandwidth,

electronic tunability, high accuracy, capability of providing rail

to rail

operation etc.

We have also included some architecture which exhibits some novelty of design

approach such as the use of new current mirror formulations or converting

transconductors into current conveyors or realizing CCs using CMOS invertors

etc. It may be mentioned that the CMOS implementations of other variants of the

current conveyors are not included herein; they are dealt with in a separate chapter

Search WWH ::

Custom Search