Hardware Reference

In-Depth Information

13

+V

12

17

outC

1

IB1A

IB2A

+V

+V

5X

5X

outA

11

2

14

4

16

Out2

In1

In2

10

Out1

outB

5

−V

−V

7

6

5X

5X

INA

IND

IB1B

IB2B

3

15

3

−V1

−V

8

18

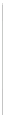

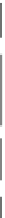

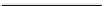

Fig. 3.18 Simplified diagram of the PA630 IC current conveyor [

19

]

3.3.2 PA630 from Phototronics Limited

In 1989, Wadsworth [

18

] reported an IC implementation of a novel CC topology

whose simplified representation is shown in Fig.

3.18

[

19

]. This IC CC was

manufactured by Phototronics Company; Ontario, Canada and took advantage of

the true complementary bipolar process technology to produce a CC IC which

offered significant improvement in the accuracy, bandwidth, transient response,

output impedance and distortion.

As can be seen from Fig.

3.18

, the basic architecture contains two base-input

mixed translinear loops which implement two on-chip voltage buffers, a basic CC

architecture and a number of current mirrors. The outside DC bias current can be set

up in both the voltage buffers as well as the basic CC by connecting external

resistors between the uncommitted terminals provided outside the chip for this

purpose one such arrangement for one of the voltage follower is shown in Fig.

3.19

where the required DC bias current is set up by an external resistor R

5

.

Figure

3.20

shows the connection of external resistors needed for biasing the CC

part of the circuit which shows how an inverting amplifier can be realized by

creating a virtual ground at pin number 7 and providing a resistor R

2

for DC biasing

of all the transistors.

Figure

3.21

shows how the CC IC PA630 can be configured as a non-inverting

amplifier together with the required DC biasing circuitry [

7

]. From the value and the

directions of the various currents shown in the diagram it is seen that same current

(I

B

+i

x

) flows in transistors Q

1

-Q

2

-Q

4

-Q

5

. Therefore, the base emitter drops of all

these four transistors are equal. Consequently, the sum of (V

BE4

+V

BE5)

cancels

(V

BE2

+V

BE1

) thereby, yielding V

y

¼

V

x

. At the output node, it is easy to see

that (I

B

+i

x

) is equal to (I

B

+i

z

), thereby yielding i

z

¼

V

in

¼

i

x.

Since i

z

¼

V

0

/R

2

and i

x

¼

v

x

/

R

1

¼

Vin/R

1

, the gain v

0

/v

in

becomes R

2

/R

1

. Lastly, the remaining resistors are

chosen as R

4

¼

R

1

and R

5

¼

R

3

to minimize the transistor output impedance error.

Search WWH ::

Custom Search