Hardware Reference

In-Depth Information

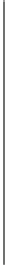

Fig. 3.15 A simplified

schematic of the bipolar

implementation of CCI+

proposed by Fabre

et al. [

14

]

+V

I

0

Q

1

Q

5

Q

2

y

z

x

Q

3

Q

6

Q

4

−V

which essentially involve the mechanism of providing a current gain between i

z

and

i

x

as explained above. As a consequence, the current transfer from X to Z port is,

therefore, given by i

z

¼

Gi

x

.

Implementation of the CCII+ with current gain described above using high

performance ALA 200 transistor arrays from ATT with circuit biased from

5V

DC power supplies and with DC bias current I

0

chosen as 50

ʼ

A, demonstrated that

G could be varied from 0.5 to 5 with the resulting

3 dB bandwidth of the current

gain remaining higher than 146 MHz. The voltage transfer between port Y and X

was found to be 0.99 with

3 dB bandwidth of 182 MHz while the input impedance

at port Y was found to be consisting of resistance R

y

¼

160 M

ʩ

in parallel with

capacitance C

y

¼

1.1 pF.

3.2.11 Bipolar Implementations of the CCI

A class AB CCI+ devised by Fabre et al. [

14

] is shown in Fig.

3.15

whose basic core

consists of two translinear mixed loops in parallel. Due to the operation in class AB

mode, the circuit can process current with magnitudes greater than the DC bias

current I

0

and therefore, generate very low harmonic distortion.

The implementation of this CCI+ using transistor arrays ALA200 from AT&T

which has NPN transistors with f

T

¼

3.5Ghz and h

FE

¼

140 and f

T

¼

2Ghz and

h

FE

¼

40 for PNP transistors it has been found that with power supply as low as

A, the circuit exhibits a bandwidth of

120 MHz, dissipates power less than 1 mW with the X-port parasitic input resis-

tance of the order of 17

1.2 V and DC bias current I

0

as 100

ʼ

. The circuit clearly is a good choice for low voltage and

low power applications requiring CCI+ as a building block.

ʩ

Search WWH ::

Custom Search