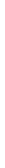

Hardware Reference

In-Depth Information

+V

a

b

e

f

N

1

N

2

c

d

g

h

I

0

Q

5

Q

6

Q

2

Q

4

Q

1

Q

3

Q

7

Q

9

Y

X

Z

Q

10

Q

8

i

j

Q

15

Q

18

Q

17

N

3

Q

16

l

k

Q

19

Q

20

−V

a

b

Q

23

Q

24

N

1

Q

21

Q

22

c

d

e

f

Q

25

Q

26

N

2

Q

27

Q

28

g

h

i

j

Q

12

Q

11

Q

14

N

3

Q

13

k

l

Fig. 3.12 CCII implementation with increased input impedance at port-Y [

12

]

composed of the DC bias current I

0

and a time varying input current signal I(t),

application of translinear principle on the loop consisting of Q

3

-Q

1

-Q

2

-Q

4

results in

the following equation:

ð

I

0

þ

It

ðÞ

Þ

I

a

¼

I

b

I

out

ð

3

:

10

Þ

Search WWH ::

Custom Search