Hardware Reference

In-Depth Information

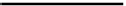

Fig. 3.1 Simplified form of

the translinear CC proposed

by Fabre [

1

]

+V

+V

Q

7

Q

8

I

1

I

2

I

2

Q

1

Q

2

i

y

i

x

i

z

Y

X

Z

Q

3

Q

4

I

4

I

3

I

4

Q

5

Q

6

−V

−V

3.2.1 Fabre

s Translinear CC

'

The core of Fabre

sCC[

1

] consists of a four transistor cell which is now commonly

referred to as the

mixed translinear cell

as it consists of two PNP transistors Q

3

and

Q

4

and two NPN transistors Q

1

and Q

2

. Assuming matched transistors with large

'

β

(hence, negligible based currents), the application of the translinear principle on the

translinear loop consisting of Q

1

-Q

2

-Q

3

-Q

4

(Fig.

3.1

) gives the equation: I

1

I

3

¼

I

2

I

4.

Since I

3

¼

(I

1

+i

y

) and I

4

¼

(I

2

+i

x)

¼

(I

2

+i

z

) and since I

1

and I

3

are identical, it

follows that i

y

¼

0. Also, for peak-to-peak input currents i

x

smaller than the bias

current, it can be seen that the translinear loop ensures that v

x

¼

i

x

follows from the assumption that pnp and npn current mirrors have unity current

transfer ratios.

It has been shown by Fabre [

1

] that the output port of his CCII has output

impedance consisting of a resistance of R

0

in parallel with capacitance C

0

. For this

CCII+ implementation experimental measurements made at 100 Hz indicated that

the equivalent resistance looking into the port-Y is dependent upon the DC bias

current, for instance, its value is 100 K

v

y

and lastly, i

z

¼

ʩ

for bias current of 330

ʼ

A and 40 K

ʩ

for

bias current of 1 mA.

With two identical Z outputs available, which requires only addition of one PNP

and one NPN transistor, such dual output CCII+ s can be used to realize a CCI+,

CCI

and CCII

as per schematics of Fig.

3.2

.

Search WWH ::

Custom Search