Hardware Reference

In-Depth Information

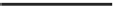

Fig. 14.17 Tunable

MOSFET-C FDNR

realization proposed by

Kacar et al. employing a

single DXCCII (Adapted

from [

38

]

©

2010 Elsevier)

C

1

z

2

y

Dual-X

CCII+

x

1

Z

in

R

z

1

x

2

V

c

C

2

μ

n

C

ox

L

V

c

C

2

which is tunable through the control voltage V

c

.

The circuit was used to design a fifth order elliptic filter design requiring two

grounded FDNRs which were simulated from the circuit of Fig.

14.17

using TSMC

CMOS 0.35

D

¼

ð

V

th

Þ

1.5 V

DC. The filter was designed for a cut-off frequency of 1.59 MHz and worked well.

μ

m process model parameters with DXCCII biased with

14.16 DXCCII-Based Grounded Inductance Simulation

Another single DXCCII-based grounded inductance simulator

3

was proposed by

Kacar and Yesil [

34

] using two resistors and a capacitor. Assuming ideal charac-

teristics of the DXCCII, a routine circuit analysis of the circuit shown in Fig.

14.18

yields the following expression for the input admittance:

2

sC

1

R

1

R

2

ð

R

1

4

R

2

Þ

Y

in

¼

ð

14

:

34

Þ

R

1

R

2

Now if we select

R

1

¼

4

R

2

, the input impedance becomes Z

in

¼

(sCR

1

R

2

/2), thus, an

inductance of value L

eq

¼

(C

1

R

1

R

2

/2) has been simulated.

The circuit was tested [

39

] in SPICE using the CMOS DXCCII from [

57

] in the

design of a 3rd order Butterworth high pass filter and a band pass filter, both

requiring one grounded inductor. The CMOS DXCCII was biased with

1.5 V

DC supply with MOS transistors simulated using TSMC CMOS 0.35 process. The

circuit was designed for f

0

¼

1.59 MHz. The simulation results agreed well with the

expectations.

3

For an interesting work demonstrating the use of DXCCII in realizing a number of positive/

negative, lossy/loss-less inductance simulation circuits, see [

34

].

Search WWH ::

Custom Search