Hardware Reference

In-Depth Information

V

in2

V

in1

V

in4

V

in3

I

in1

I

G2

R

2

I

in2

I

G3

I

G1

R

1

R

3

V

out

I

in3

I

x(DDCC1)

I

x(DDCC3)

I

x(DDCC2)

I

out

y

1

x

V

in6

y

1

x

y

1

x

DDCC(1)

z

1

−

z

2

−

DDCC(2)

DDCC(3)

y

2

V

in5

y

2

y

2

y

3

y

3

z+

z−

y

3

z−

I

z−(DDCC2)

I

z2−(DDCC1)

I

z+(DDCC1)

I

z−(DDCC3)

C

2

C

1

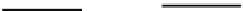

Fig. 12.22 Mixed-mode VM universal biquad proposed by Lee [

51

]

N

2

s

ðÞ¼

sC

1

I

in

1

þ

ð

I

in

2

Þ=

R

2

þ

ð

I

in

1

I

in

3

Þ=

R

1

R

2

ð

12

:

85

Þ

s

2

C

1

C

2

I

in

1

N

3

s

ðÞ¼

sC

1

I

in

2

ð

Þ=

R

2

þ

I

in

3

=

R

1

R

2

ð

12

:

86

Þ

and

s

2

C

1

C

2

þ

ðÞ¼

sC

1

=

R

2

þ

=

R

1

R

2

ð

:

Þ

Ds

1

12

87

In [

51

], it has been shown that the circuit can realize a large variety of filter

responses, in CM, VM transadmittance mode and transimpedance mode. For the

details of all these special cases, the reader is referred to [

51

].

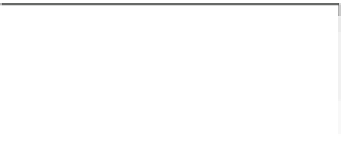

Tangsrirat-Channumsin-Pukkalanun biquad In 2013 Tangsrirat et al. [

65

] pro-

posed a high input impedance resistorless realization of electronically tunable VM

single input five outputs (SIFO) type universal filter configuration using three

DDCC transconductance amplifiers (DDCCTAs) and two grounded capacitors.

The circuit offers the realization of all the standard filter functions simulta-

neously without any component matching condition. An ideal DDCCTA can be

characterized by the following hybrid matrix:

2

4

3

5

2

4

3

5

2

4

3

5

i

y

1

i

y

2

i

y

3

v

x

i

z

i

0

000000

000000

000000

1

v

y

1

v

y

2

v

y

3

i

x

v

z

v

0

¼

ð

:

Þ

12

88

11000

000100

0000

g

m

0

where g

m

is the transconductance of the DDCCTA. A routine circuit analysis of

Fig.

12.23

yields the following VM transfer functions:

Search WWH ::

Custom Search