Hardware Reference

In-Depth Information

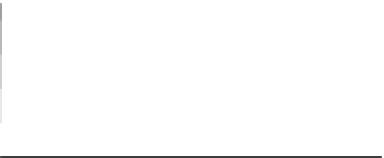

R

4

z

1

y

1

y

2

V

05

1

V

03

V

01

R

3

DVCC

V

i1

z

1

z

2

y

1

V

02

x

2

V

04

V

i3

DVCC

z

2

y

2

x

C

2

R

1

C

1

V

i2

R

2

Fig. 12.5 VM biquad filter using two DVCCs proposed by Chen and Shen [

6

]

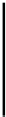

h

V

i

1

þ

n

þ

o

V

i

2

n

þ

V

i

3

o

i

R

1

R

2

R

3

s

2

C

1

C

2

1

R

3

1

R

1

R

2

1

s

2

C

1

C

2

1

R

2

1

R

2

R

3

sC

2

sC

1

V

04

¼

DðÞ

ð

12

:

14

Þ

h

R

3

V

i

1

þ

n

R

2

R

2

R

3

V

i

3

o

i

s

2

C

1

C

2

1

ð

V

i

2

Þ

s

2

C

1

C

2

1

þ

sC

1

1

R

4

R

1

V

05

¼

Ds

ðÞ

ð

:

Þ

12

15

þ

þ

1

R

3

1

R

1

R

2

1

R

1

R

2

R

3

s

2

C

1

C

2

where D s

ðÞ¼

sC

2

ð

12

:

16

Þ

Depending upon the appropriate choice(s) of the input signal(s), the various filter

responses can be obtained through the following two cases:

Case I

(a)

If we choose V

i2

¼

V

i3

¼

0 and V

i1

¼

V

in

¼

input signal, then the following

filter functions can be obtained:

R

1

R

3

Ds

R

1

R

2

R

3

Ds

n

R

3

o

1

1

s

2

C

1

C

2

1

1

R

1

R

2

R

3

sC

2

þ

V

01

V

in

¼

V

02

V

in

¼

V

03

V

in

¼

V

04

V

in

;

ðÞ

;

;

ðÞ

Ds

ðÞ

R

3

Ds

R

3

Ds

s

2

C

1

C

2

1

s

2

C

1

C

2

1

and

V

05

R

4

R

1

¼

V

in

¼

ð

12

:

17

Þ

ðÞ

ðÞ

Thus, from the above equations, it is clear that a BPF, LPF, and notch can be

realized at V

01

,V

02

, and V

03

respectively while two HPF functions can be obtained

at V

04

and V

05

respectively.

Search WWH ::

Custom Search