Hardware Reference

In-Depth Information

I

Z

a

C

C

±K

I

X

A

V

Y

G

M1

−A

V2

VF

V

X

R

01

G

M2

b

+V

DD

M

10b

M

9b

V

IT+

M

2

M

4

M

7

C

c

R

C

M

9

M

10

M

16b

M

7b

M

10c

M

8

V

b1

M

3

M

6

Y

M

1

Z

X

M

5

M

15c

M

14c

V

B3

M

16

M

13b

M

15

M

15b

M

14

M

14b

V

B1

V

B1

V

vt+

M

11

V

vt−

V

B2

M

13

M

12

V

IT−

−V

SS

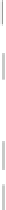

Fig. 10.22

The architecture and implementation of the VCG-CCII proposed by Marcellis et al. (

a

)

Block diagram (

b

) An exemplary CMOS implementation (Adapted from [

60

]

©

2009 Springer)

The three ports of the inherent CC are created as follows: A voltage follower

between ports Y and X is created by two transconductance stages, an internal

frequency compensation circuit and a voltage follower. Since the input front end

is a transconductor, its very high input impedance would imply I

y

¼

0. The output

current of the voltage follower, which constitutes I

x

,

is

sensed through the technique

of power-supply-current-sensing technique applied on this voltage follower and

accordingly, the port Z is created. The two transconductors along with the com-

pensating circuitry and VF ensure that the voltage gain between ports Y and X is

electronically-controllable

by

the

ratio

of

the

transconductances,

since

V

x

/V

y

¼

G

m1

/G

m2

. The input impedance looking into the port Y is ideally infinite

leading to I

y

¼

0.

For some other, digitally-controlled Current Conveyor versions, the reader is

referred to [

61

,

62

].

Search WWH ::

Custom Search