Hardware Reference

In-Depth Information

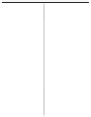

+V

DD

M

5

M

6

M

8

M

7

M

3

M

4

Y

3

X

Z

M

1

Y

1

M

2

Y

2

I

B

I

B

I

B

I

B

V

bias

M

12

M

9

M

10

M

11

−V

SS

Fig. 10.8

An exemplary CMOS DDCCII+

differential current two a single ended output current in the MOSFET M

7

. The

output voltage of this amplifier is given by:

V

X

¼

A

0

V

Y1

½

ð

V

Y2

Þ

ð

V

G3

V

Y3

Þ

ð

10

:

5

Þ

where A

0

is the open loop gain of the amplifier and V

G3

is gate voltage of MOSFET

M

3

.

The relation between the four voltages can be expressed as:

A

0

A

0

þ

V

X

¼

1

V

Y

1

ð

V

Y

2

þ

V

Y

3

Þ

V

Y

1

V

Y

2

þ

V

Y

3

ð

10

:

6

Þ

Lastly, it can be readily seen that both i

x

and i

z

flow simultaneously and equally

towards or away from the DDCC thereby leading to i

z

¼

+i

x

and the circuit realizing

a DDCC+. It may be mentioned that a DDCC

can be easily realized by appro-

priate addition of another pair of MOSFET current mirrors.

An attractive feature of the DDCC is its capability of realizing summation or

subtraction of the signals without requiring any external resistor as reflected from

the equation:

V

X

¼

ð

V

Y

1

V

Y

2

þ

V

Y

3

Þ

ð

10

:

7

Þ

That DDCCIIs are particularly attractive for evolving single resistance controlled

sinusoidal oscillators employing all grounded passive elements, has been demon-

strated in [

10

]. On the other hand Current-controllable versions of DDCC, known as

CCDDCC implementable in CMOS as demonstrated in [

11

], are useful in devising

grounded-capacitor based floating capacitance multiplier and Current-mode uni-

versal filter [

11

].

Search WWH ::

Custom Search