Hardware Reference

In-Depth Information

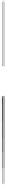

Fig. 6.22 Another VM

filter with three inputs and

one output proposed by

Chang and Lee [

20

] which

is obtained by removing one

redundant CCII-from the

circuit of Fig.

6.21

V

in2

V

in1

C

1

R

1

1

V

0

V

in3

y

y

z

R

2

z

x

C

2

x

CCII+

CCII+

R

3

which can realize all the five standard filter functions. This circuit is shown in

Fig.

6.23

.

Assuming ideal CCII

, the expressions for V

01

and V

02

in terms of its inputs can

be derived as:

s

2

C

1

C

2

þ

R

3

V

i

1

þ

V

i

2

þ

R

2

R

3

V

i

3

1

∇

V

01

¼

sC

1

=

sC

2

=

R

1

1

=

sC

2

=

R

1

s

2

C

1

C

2

þ

R

2

V

i

1

V

i

3

1

∇

V

02

¼

sC

1

=

sC

1

=

R

1

þ

sC

1

=

R

2

þ

sC

2

=

R

1

þ

1

=

R

1

R

2

R

1

R

2

þ

V

i

2

þ

1

=

sC

2

=

R

1

þ

sC

1

=

R

1

s

2

C

1

C

2

þ

where

∇

¼

sC

1

C

2

=

R

3

þ

1

=

R

2

R

3

ð

6

:

34

Þ

Thus, the various filters can be realized as follows: (i) for V

i1

¼

0 (grounded) and

V

i2

¼

V

i3

¼

V

in

, LPF can be realized at V

01

and BPF at V

02

; (ii) for V

i1

¼

V

i3

¼

0

and V

i2

¼

V

in

, a BPF can be obtained at V

01

; (iii) for V

i1

¼

V

i3

¼

V

i2

¼

V

in

, a HPF

can be realized at V

02

; (iv) for V

i2

¼

0, V

i1

¼

V

i3

¼

V

in

and C

2

R

3

¼

C

1

R

1

, a notch

can be obtained at V

01

; (v) for V

i2

¼

0, V

i1

¼

V

i3

¼

V

in

and C

2

R

3

¼

R

1

(2C

1

+C

2

),

an APF can be obtained at V

01

.

Using CCII-implementable in 0.35

1.65 V DC

power supplies, the circuit has been observed to realize all the five filters with f

0

of

the order of 1 MHz. The simulation results were found to be in close conformity to

the theoretical ones. However, in actual hardware, the circuit can also be realized

using two AD844 ICs to realize the CCII

ʼ

m CMOS process, biased with

Chang Universal Biquad Figure

6.24

shows a two input three output multi-

function biquad presented by Chang [

17

].

The expressions for the three outputs in terms of the two inputs (assuming ideal

CCIIs) are found to be:

Search WWH ::

Custom Search