Hardware Reference

In-Depth Information

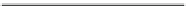

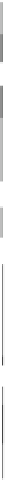

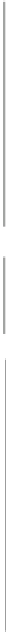

+V

DD

I

r2

Ir1

M

rP2

M

rP1

M

rN2

MrN1

M

OP

M

N2

M

OPC

MA

M

N1

V

Y

M

O

V

Y

I

BIAS

V

Z

V

X

M

p1

V

Y

M

ONC

M

p2

M

ON

M

B

M

rp3

M

rp4

M

rN3

M

rN4

I

r4

I

r3

−V

SS

Fig. 4.13 CC proposed by Kasemsuwan and Nakhlo [

52

]

channel inversion layer. Thus, a bulk-driven MOSFET can effectively work under

negative, zero or even slightly positive biasing conditions.

Khateb et al. [

60

] proposed a CCII architecture using a folded-cascode bulk-

driven OTA structure consisting of transistors M

1

-M

11

where M

1

-M

2

constitute the

input stage, M

6

-M

7

provide a level shift stage and the MOSFETs M

8

-M

8c

,M

9

-M

9c

constitute a cascode current mirror which performs the operation of differential to

single-ended conversion (Fig.

4.14

). The MOSFETs M

3

-M

4

provide the current

necessary for the input and output branches. The transistors M

10

-M

11

constitute the

second stage of the OTA. Transistors M

12

-M

13

and M

14

-M

15

are identical to

transistors M

10

and M

11

respectively. Since the gates of M

11

,M

13

and M

15

,M

10

and M

12

,M

14

are tied together, the currents in the branches M

10

-M

11

,M

12

-M

13

an

M

14

-M

15

are necessarily same.

The simulation results of this low-voltage, low-power bulk-driven CCII demon-

strate that both the current and voltage ratios are

exactly unity

with the 3 dB

bandwidth in excess of 10 MHz, with DC biasing voltage as low as 0.38 V the

Search WWH ::

Custom Search