Biomedical Engineering Reference

In-Depth Information

1

Defect-oblivious

routing-aware

0.8

0.6

0.4

Defect-tolerant

routing-aware

0.2

0

200

250

200

400

150

100

Upper Limit on

Completion Time

600

Minimum Routable

Chip Area

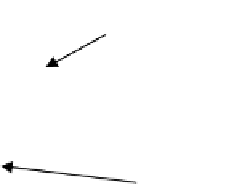

Figure 2.11

Feasibility frontier surface and feasible design region for defect-tolerant and defect-oblivious

routing-aware synthesis methods.

F

m

<

F

G

. A feasibility frontier surface is obtained by connecting all the fea-

sibility boundary points as shown in Figure 2.11. The feasible design region

corresponds to the space above the feasible surface. Any design specification

whose corresponding point is located in this region can be met. Otherwise,

no feasible design exists for this specification.

As shown in Figure 2.11, defect-tolerant routing-aware synthesis leads to a

lower-feasibility frontier surface and a larger feasible design space than the

defect-oblivious method. For tight time and area limits (e.g., 400 s, 110 elec-

trodes), the defect-tolerant method achieves a routable synthesis result with

failure rate less than 0.5, while the defect-oblivious method requires a failure

rate of at most 0.1. On the other hand, for a predetermined failure rate limit

(e.g., 0.3), defect-aware synthesis leads to a much lower assay completion

time (less than 390 s) and smaller chip area (less than 100 electrodes) than

the defect-oblivious method, which requires a completion time of 450 s and

a minimum chip area of 150 electrodes. The improvement becomes more

significant for limits on the failure rate. Defect-aware synthesis allows us to

reduce chip area and assay completion time, and thereby the product cost for

reliable biochip platforms.

2.5 Chapter Summary and Conclusions

We have presented a droplet-routing-aware automated synthesis tool for

microfluidic biochips. Droplet routability, defined as the ease with which