Hardware Reference

In-Depth Information

credit

update

pipeline

register

outAvailable[0...N-1]

outPort

ready out[0...N-1]

CC

RC

SU

req

en

dst

Head flit

moves forward

SA

outLock

1

en

head

credit update

head

ready

granted

valid

data

valid

data

ST

valid

data

Input #i

Output #j

Pipelined

Elastic Buffer

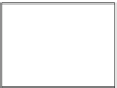

Fig. 5.7

The organization of a router that pipelines RC from SA and ST using a pipeline register

both it the control and in the data path of the router. The pipeline register of the datapath acts as an

1-slot EB that holds the flits ready for request generation and SA

the old packet that lies in the EB tries to reset the

outPort

register and leave the EB,

priority is given to the head flit of the new packet. Notice that the

outPort

register

is protected, so that a previous packet's saved request is not overwritten by the head

flit of the next packet. If a tail is stalled at the intermediate EB (e.g. if all of the

output buffer's slots where occupied), setting a new value to the

outPort

register by

a head flit at the input buffer would not be allowed.

The intermediate EB acts as an extension of the input FIFO buffer. It receives the

grants produced by SA instead of the main input buffer and guides the generation of

the credit update signals send to the upstream connections. A credit update is sent

backwards, not when a flit leaves the input buffer, but instead, when it leaves the

intermediate 1-slot EB. Keep in mind that now, the input buffer can actually hold

b

C

1 flits (b in the main input buffer plus 1 in the intermediate EB), implying that

the credit counter responsible for counting the free slots of this input (e.g. at the

output of the adjacent router), must have a maximum value of b

C

1, instead of b.

An example of the operation of a router that includes both control and data

pipeline segments is depicted in Fig.

5.8

using the same flow of flits as in the

previous example, where pipelining of the RC stage was done only in the control

path. The first true difference between the two cases appears in cycle 1. The head flit

once it completes RC it is dequeued from the input buffer and moves to the pipelined

EB. The head flit will wait there until it wins in SA and moves to its selected output.

As long as the head flit is stalled in the pipelined EB stage all the rest flits are stalled

inside the input buffer.

In cycle 2 two operations occur in parallel. The first one involves the operations

of the head flit that participates in SA, wins a grant, consumes a credit, updates the

outAvailable

flag, and gets dequeued from the intermediate EB moving towards its

destined output port via ST. The second one involves the operation of the body flit

that moves from the input buffer to the intermediate 1-slot EB. The intermediate EB

Search WWH ::

Custom Search