Hardware Reference

In-Depth Information

3.1.1

Credit-Based Flow Control at the Output Link

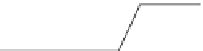

The baseline architecture involves a buffer at the output module as well as an

optional intermediate one. Assuming that the intermediate buffer is not present

we can re-draw the microarchitecture of the primitive switching element following

the abstract flow control model developed in Chap.

2

. In this case, illustrated in

Fig.

3.4

a, the output buffer consists of a data buffer and a free slots counter that

is updated by the output buffer for increasing its value and by the incoming valid

signals from the output of the multiplexer for reducing its value.

a

ready

slot

counter

-

+

outAv

ailable

outLock

request

generation

arb

update

valid

data

Input #0

from/to other input(s)

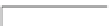

b

credit

counter

ready

-

+

arb

update

valid

data

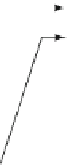

c

credit

counter

ready

-

+

arb

update

valid

data

Fig. 3.4

The changes required in order for the switching module to connect to a credit-based flow

controlled link. The output of the switching module may include an additional pipeline register for

isolating the internal timing paths from the link

Search WWH ::

Custom Search