Hardware Reference

In-Depth Information

FIFO

tail

head

push

pop

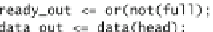

ready_out

ready_i

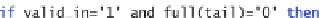

n

valid_out

valid_in

data_out

data_in

Fig. 2.10

The organization of a FIFO queue using many HBEBs in parallel and indexing the push

and pop operations via the tail and head pointers

with new data once the output EB becomes full. During a read the output interface

checks only the words stored in the EB. When the output EB becomes empty,

automatically data is transferred from the parallel FIFO to the output EB without

waiting any event from the output interfaces. The output EB should be seen as an

extension of the capacity of the main FIFO by two more positions.

For large FIFOs the buffer slots can be implemented by a two-port SRAM array

that supports two independent ports one for writing (enqueue) and one for reading

(dequeue). The read and write addresses are driven again by the head and tail

pointers and the control FSM produces the signals needed to interface the FIFO

Search WWH ::

Custom Search