Hardware Reference

In-Depth Information

2.1.2

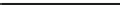

Full-Bandwidth 2-Slot Elastic Buffer

The throughput limitation of HBEB can be resolved by adding two of them in each

EB stage and using them in a time-multiplexed manner. In each cycle, data are

written in one HBEB and read out from the second HBEB thus giving the impression

in the upstream and the downstream channel of 100 % of write/read throughput.

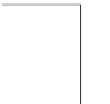

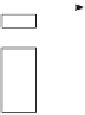

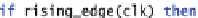

The design of the 2-slot EB that consists of two HBEBs needs some additional

control logic that indexes the read and writes position; the organization of the 2-slot

EB is shown in Fig.

2.6

along with its abstract VHDL description. When new data

2-slot EB

tail

head

write

read

EB

in_ready

out_rea

d

y

out_valid

in_valid

out_data

in_data

Fig. 2.6

The organization and the abstract VHDL description of a full-throughput 2-slot EB using

two HBEBs in parallel that are accessed in a time interleaved manner as guided by the head (for

read) and tail pointers (for write)

Search WWH ::

Custom Search