Hardware Reference

In-Depth Information

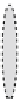

read

ready_in

R

Q

valid_out

S

write

valid_in

ready_out

en

DQ

data_in

data_out

Fig. 2.4

The primitive 1-slot elastic buffer

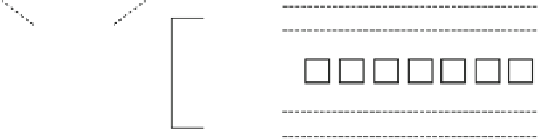

cycle

r

v

D

0

1

2

3

4

5

6

write side read side

1

1

A

0

1

B

1

1

B

0

1

C

0

1

C

1

1

C

0

1

D

Write

Side

r

r

v

v

EB

*

A

*

B

B

*

C

r

v

D

1

0

*

1

1

A

1

0

*

0

1

B

1

1

B

1

0

*

1

1

C

D

D

Read

Side

Fig. 2.5

Data transfer between two flow-control channels connected via a half-bandwidth elastic

buffer

using simple registers after deciding on how the circuit will function when R

and S are both asserted (giving priority to R, giving priority to S or keeping the

register's old value). For the implementation shown in Fig.

2.4

, we assume that set

(write) has the highest priority although read (R) and write (S) cannot be asserted

simultaneously.

The presented EB allows either a push or a pop to take place in each cycle,

and never both. This characteristic imposes 50 % throughput on the incoming and

the outgoing links, since each EB should be first emptied in one cycle and then

filled with new data in the next cycle. Thus, we call this EB a Half-Bandwidth EB

(HBEB). A running example of data transfers that pass through a HBEB is shown

in Fig.

2.5

. The HBEB, although slower in terms of throughput, is very scalable in

terms of timing. Every signal out of the HBEB is driven by a local register and

no direct combinational path connects any of its inputs to any of its outputs, thus

allowing the safe connection of many HBEB in series.

Search WWH ::

Custom Search