Hardware Reference

In-Depth Information

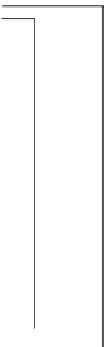

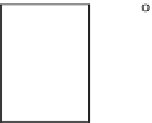

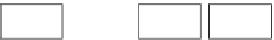

SU

outVCAvailable

SA req

VA

SA

VA

req

RC

"0...00"

ready VC

candidateOutVC

en

en

outPort[i]

outVC[i]

RC

deMUX

en

from other

VCs of the

same input

dst

head

CC

credit

update

outVCLock[i]

head

replace VC id field

SU

ready

valid

data

Pipelined

Elastic Buffer

ST

en

Input VC #i

from other VCs

of the same input

from other inputs

Output #j

Fig. 9.17

The 4-stage pipelined organization of the VC-based router that executes RC, in the first

pipeline stage, VA in the second, SA in the third and ST in the last pipeline stage. The critical

path of the design is expected to be either at the VA or the SA stage, depending on the number

of input/output ports of the router and the number of VCs. As a first thought, VA should be more

delay critical than SA due to the larger arbiters involved in its operation. However, the delay of SA

is significantly augmented by the more involved request distribution and grant handling logic that

brings its final delay very close to that of VA

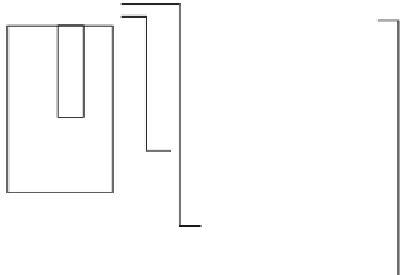

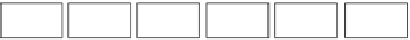

0

1

2

3

4

5

6

7

8

9

cc

VA

su

H

LT-BW

RC-EB

SA-DQ

LT-BW

ST

cc

B

LT-BW

EB

SA-DQ

LT-BW

ST

cc

T

LT-BW

EB

SA-DQ

LT-BW

ST

VA

su

cc

H

LT-BW

RC-EB

SA-DQ

LT-BW

ST

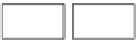

Fig. 9.18

An example of the operation of the 4-stage pipelined router RC|VA|SA|ST for the flits

of two packets arriving back-to-back at the same input VC

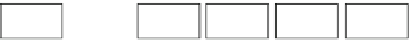

move to the corresponding per-input data pipeline register of the crossbar. The body

flit that follows takes its place in the intermediate EB. At the same time, the head flit

of the next packet arrives at the same input VC, while the tail flit of the first packet

remains in the input VC buffer. As the head flit is written to the output pipeline

register and consumes a credit, in cycle 4, the body flit moves at the input of the

crossbar, and the EB of the same input VC is refilled with the tail flit. The following

packet's head flit is unable to do anything, since it has not reached the frontmost

position of the input VC buffer yet. This idle cycle translates to a bubble on the

input's outgoing traffic, which is unavoidable when all traffic arrives on the same

input VC.

Search WWH ::

Custom Search