Hardware Reference

In-Depth Information

9.4

The Switch Allocation Pipeline Stage

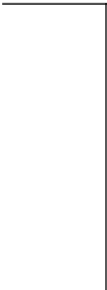

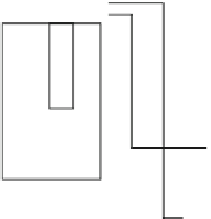

Switch allocation is the last step that a flit is required to take before traversing the

crossbar (switch traversal) and reaching the output pipeline register. The SA unit

produces in each cycle the grants that are used to dequeue the winning flits from

their input VC buffers, and to setup appropriately the select lines of the per-input

and the per-output multiplexers of the router. In order to isolate the delay of SA

from the delay of ST we need to add pipeline registers at the select lines of the per-

output multiplexers of the crossbar as well as at each data input of the crossbar. This

pipelined organization is shown in Fig.

9.11

.

The pipeline registers at the data path of the router are actually added at the output

of the per-input multiplexers and they are loaded with new data only if an input VC

that belongs to that input is granted in SA. Once data reach that point, they cannot

stall, since they are heading to an already allocated output VC that has for sure

enough credits (both conditions have been checked during the request generation of

SA).

The router's operation, when RC-VA-SA are isolated from switch traversal using

pipelining, is illustrated in Fig.

9.12

. In cycle 0, a head flit is written to the input

VC buffer and executes successfully all allocation stages in cycle 1. Thus, in the

same cycle it is dequeued and moves to the data pipeline register at the input of the

crossbar. In parallel, the crossbar's select signals are also registered, so that the head

flit can switch to the proper output port (ST) and consume a credit from the proper

output VC (CC), in cycle 2.

SU

outVCAvailable

VA

SA

SA req

RC

VA req

"0...00"

ready VC

candidateOutVC

en

outPort[i]

outVC[i]

RC

deMUX

from other

VCs of the

same input

en

dst

credit

update

CC

head

outVCLock[i]

SU

ready

valid

data

replace VC id field

ST

en

Input VC #i

from other VCs

of the same input

from other inputs

Output #j

Fig. 9.11

The router's organization that separates SA stage from ST in a pipelined manner. RC,

VA and SA are performed in the first pipeline stage and in the next stage the flits move to ST and

reach the corresponding output link one cycle later. The pipeline registers added at the input of ST

are not flow controlled and outgoing data cannot stop there and are always forwarded in the next

cycle

Search WWH ::

Custom Search