Hardware Reference

In-Depth Information

flow of flits inside the pipeline. The second option pipelines also the datapath of the

router, allowing more than one flits per input VC to execute their tasks in parallel,

and thus removing the idle cycles experienced by the flits of a packet.

9.2.1

Pipelining the Router Only in the Control Path

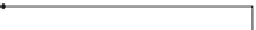

The RC is stage is separated from the rest stages of the router via the

outPort

Œi

register available per input VC. In the single-cycle organization this register is

bypassed via a multiplexer when a head flit appears at the frontmost position of the

input VC buffer. This bypass is necessary for allowing the head flit to generate the

requests to the VA in the same cycle. In the RC pipelined organization, illustrated in

Fig.

9.4

, this bypass multiplexer is removed allowing the

outPort

register to play

the role of the pipeline register in the control path that separates RC from VA,

SA and ST. In the case that routing computation guides also the generation of the

candidateOutVC

vector for each input VC, an additional pipeline register should be

added to those signals as well, as shown in Fig.

9.4

. Both pipeline registers storing

outPort

and

candidateOutVC

are set when the head flit of the packet appears at the

frontmost position of the input VC buffer, and, they reset, when the tail flit of the

packet is dequeued from the input VC buffer.

An example of the operation of a pipelined router that executes RC and VA-SA-

ST in different cycles is depicted in Fig.

9.5

. A head arrives in cycle 0 and appears

at the frontmost position of the input VC buffer in cycle 1. Routing computation

SU

outVCAvailable

VA

SA

VA

req

SA req

RC

"0...00"

ready VC

θ

1

candidateOutVC

θ

1

en

outVC[i]

RC

deMUX

outPort[i]

en

CC

dst

credit

update

head

outVCLock[i]

SU

replace VC id field

read

valid

data

ST

Input VC #i

from other VCs

of the same input

from other inputs

Output # j

Fig. 9.4

The organization of a 2-stage pipelined VC-based router that pipelines routing computa-

tion from the rest tasks of the router. The pipeline registers are added after RC only in the control

path of the router. Additional pipeline registers are not required and the

outPort

Œi register, or

possibly the

candidateOutVC

Œi register, play the role of the pipeline registers after removing the

bypass path that exists in the single-cycle VC-based router implementation

Search WWH ::

Custom Search