Hardware Reference

In-Depth Information

0

1

2

3

4

5

cc

H

LT - BW

RC-VA-SA-DQ-ST

LT - BW

su

B

T

H

cc

SA-DQ-ST

LT - BW

LT - BW

cc

SA-DQ-ST

LT - BW

LT - BW

LT - BW

su

cc

RC-VA-SA-DQ-ST

LT - BW

su

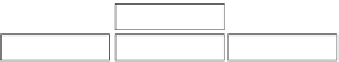

Fig. 9.2

An example of the operation of a single-cycle VC-based router that receives the flits of

two packets from the same input VC in consecutive cycles. Each flit spends one cycle inside the

router for completing all the required tasks and one cycle on the link that connects two neighbor

routers

Since the input VC has not yet allocated an output VC (

outVCLock

Œi

D

0), it is

allowed to send a new output VC request to the VC allocator, which in turn,

successfully assigns an output VC from the available ones. The newly assigned

output VC is marked as unavailable (State Update - SU) and is used by the matched

input VC to generate a request to the switch allocator (SA). The flit wins in both

arbitration stages (SA1, SA2) and gets dequeued (DQ) from the input VC buffer,

eventually crossing both the per-input VC and the per-output multiplexers of the

router's datapath. As the flit is about to be written to the output pipeline register,

the credit controller reads the flit's output VC id and decreases its value (Credit

Consume - CC).

The next (body) flit arrives in cycle 1 and appears at the frontmost position of the

same input VC buffer in cycle 2, following the dequeue of the head flit. Therefore,

while the head flit crosses the link and is stored at the VC buffer of the next router,

the body flit inherits both the destined output port and the allocated VC, set in

the previous cycle by the head flit, and immediately performs SA. The body flit

is granted in the same cycle and is dequeued from the input VC buffer moving

towards the output pipeline register. When the body flit reaches the selected output

it decrements the corresponding credit counter using the id of the allocated output

VC.

The same procedure is followed by the tail flit of the packet in cycle 3. Since the

departing flit is the last flit of the packet, all state variables are reset at the input VC

side (

outPort

Œi ,

outVCLock

Œi ,

outVC

Œi ). The existence of a tail flit is also detected

at the output side, indicating that the output VC pointed by the flit's VC id should

be released as well (SU). Therefore, the head flit of the next packet, which arrives in

cycle 3, finds all resources available and can initiate the execution of all the required

tasks without experiencing any idle cycle irrespective of its destined output port.

9.1.2

Example 2: Two Packets Arriving at Different Input VCs

Another example of the router's cycle-by-cycle operations is presented in Fig.

9.3

,

where two packets arrive in the same input, but interleaved in different input VCs.

Search WWH ::

Custom Search