Hardware Reference

In-Depth Information

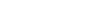

Fig. 7.12

(

a

) An example of

the request and grant matrix

of switch allocation, and (

b

)

its equivalent bipartite graph

representation. Although

every input VC can request

any output, only one VC per

input can be granted

a

Requests

SA Grants

VC#0

VC#1

VC#2

VC#3

VC#4

VC#5

Output Ports

b

VC

#0

VC

#0

VC

#1

VC

#1

Out

#0

Out

#0

VC

#2

VC

#2

Out

#1

Out

#1

VC

#3

VC

#3

Out

#2

Out

#2

VC

#4

VC

#4

VC

#5

VC

#5

7.2.4

Gathering Grants and Moving to the Output

The switch allocator's decisions are distributed in the same cycle to the input

controllers and the crossbar. Each input VC receives a flag bit showing if it has

won access to the selected output port or not. Once granted, the corresponding input

VC dequeues its flit from the input VC buffers, and sends a credit update backwards,

informing that a buffer slot is emptied. The multiplexer that selects only one input

VC per input is also driven by the switch allocator's output, so that only the selected

input VC to reach the crossbar. On dequeue, the flit updates its VC id field by using

theidstoredinthelocal

outVC

Œi variable (or the one just returning from the VC

allocator). If a tail flit is preparing to leave the i th input VC, then it should de-

allocate all resources reserved per packet at the input controller, such as the state

variables

outPort

Œi ,

outVCLock

Œi and

outVC

Œi .

The crossbar knows how to handle the incoming flits from all input controllers

since the switch allocator has transferred to the crossbar the switching configuration

of the current cycle that describes the connections between inputs and outputs. As

the flit traverses the crossbar and moves to the output pipeline register, its VC ID

field is used to decrement appropriately

creditCounter

Œ

VCid

. In the next cycle, the

flit is forwarded to the link where it cannot be stopped, since credit availability has

been checked before it was allowed to participate in switch allocation. In the case

Search WWH ::

Custom Search